## **SmartDesign User Guide**

Libero SoC v2025.2

#### Introduction (Ask a Question)

The SmartDesign tool is a visual block-based design creation and entry tool for instantiating, configuring, and connecting Microchip IPs, user-generated IPs, and custom and glue-logic HDL modules. The tool provides a canvas for stitching together the various design components.

The resulting HDL from the SmartDesign tool is a Design-Rule-Checked (DRC) and synthesis-ready HDL file. A generated SmartDesign can be the entire FPGA design or a component subsystem to be reused in a larger design.

The SmartDesign canvas instantiates the following design objects:

- Microchip IP cores

- User-generated or third-party IP cores

- HDL modules

- HDL parameterized core modules

- Basic macros

- Other SmartDesign components

- Reusable design blocks published from the Libero® SoC Design Suite

The SmartDesign tool provides the following features for effortless design creation and visualization:

- Addition of synthesis attributes to design objects

- · Visualization of the memory map of the design

- Smart Search and Connect tool for fast design look-up and connectivity for complex designs

- Smart Search and Filter to create focused cones of the design on the canvas

## **Table of Contents**

| Intr | oductior | 1                                                                | 1  |

|------|----------|------------------------------------------------------------------|----|

| 1.   | Unders   | tanding the SmartDesign Canvas                                   | 4  |

|      | 1.1.     | lick and Drag Operations in the Canvas                           | 4  |

|      | 1.2. A   | dditional Canvas Operations                                      | 5  |

| 2.   | Creating | g a Synthesizable SmartDesign                                    | 7  |

|      | 2.1.     | reating a SmartDesign Component                                  | 7  |

|      | 2.2. lı  | mporting an Existing HDL Source File(s) or Folder(s)             | 7  |

|      | 2.3.     | reating a New HDL File Using the IDE                             | 8  |

| 3.   | Instanti | ating User HDL Modules, IP Cores, and Components in SmartDesign  | 9  |

|      | 3.1. lı  | nstantiating a User HDL Module in your Design                    | 9  |

|      | 3.2. C   | reating a HDL+ Core from an User HDL Source Module               | 9  |

|      | 3.3. C   | Configuring and Instantiating Instances in your Design           | 10 |

|      |          | eplacing an Instance Component with a Different Component        |    |

|      |          | Ipdating a Component Core Version                                |    |

|      |          | Ipdating the Component Instance Port List                        |    |

|      | 3.7. P   | erforming Additional Operations on Components                    | 16 |

| 4.   | Creating | g Pins and Ports for Connecting Instances in the SmartDesign     | 18 |

|      | 4.1. C   | reating Pins and Ports for your Design                           | 18 |

|      | 4.2. N   | Nodifying the Pin Order                                          | 19 |

|      |          | erforming Operations on Pins or Ports                            |    |

|      | 4.4. V   | Vorking with Bus and Slice                                       | 22 |

| 5.   | Connec   | ting Instances in your SmartDesign                               | 27 |

|      | 5.1. N   | Method 1: Using the Drag and Drop Feature                        | 27 |

|      | 5.2. N   | Nethod 2: Using the Right-click Menu                             | 27 |

|      |          | howing or Hiding Nets and Net Names                              |    |

|      | 5.4. P   | erforming Operations on Nets                                     | 28 |

| 6.   | Finding  | Objects in Your Project                                          | 29 |

| 7.   | Using th | ne Smart Search and Connect Tool                                 | 31 |

|      | 7.1. S   | earching for Design Objects in the Canvas                        | 32 |

|      |          | Jarrowing the Search for Design Objects Using Filters            |    |

|      | 7.3. A   | pplying the Selected Filters on the Design Objects in the Canvas | 33 |

|      | 7.4. C   | Connecting and Disconnecting the Ports or Pins                   | 34 |

| 8.   | Working  | g with Hierarchical SmartDesigns                                 | 35 |

|      | 8.1. C   | reating a Hierarchical SmartDesign                               | 35 |

|      |          | lattening a Hierarchical SmartDesign                             |    |

|      |          | xpanding and Folding Instances                                   |    |

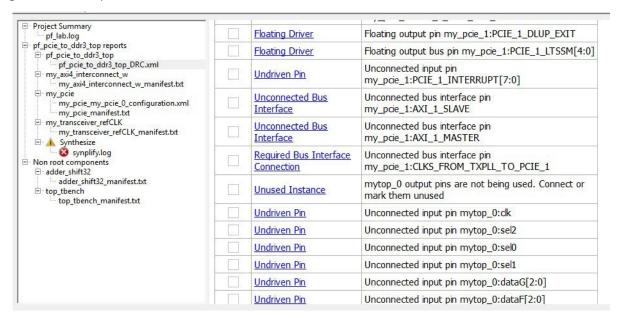

| 9.   | Validati | ng the SmartDesign Using the DRC                                 | 41 |

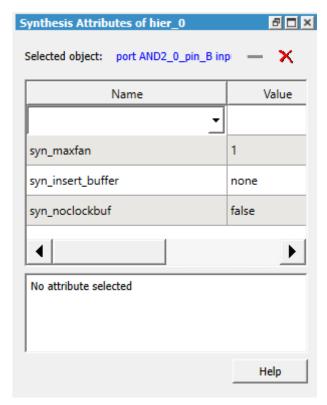

| 10.  | Managi   | ng Synthesis Attributes                                          | 4  |

|      |          |                                                                  |    |

| 11.  | Genera   | ting the SmartDesign Component                                   | 45 |

| 11.1. Generating the SmartDesign Component Recursively     | 45 |

|------------------------------------------------------------|----|

| 11.2. Generating the SmartDesign Component Non-recursively |    |

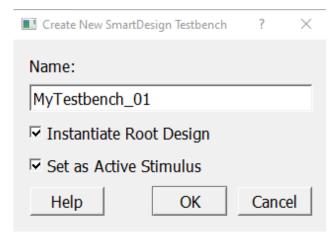

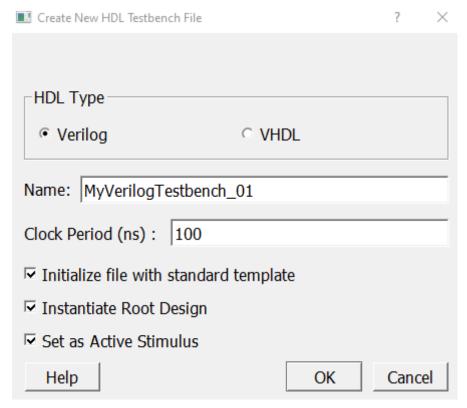

| 12. Creating a SmartDesign Testbench                       | 46 |

| 12.1. Creating a SmartDesign Testbench                     | 46 |

| 12.2. Creating a SmartDesign HDL Testbench Using the IDE   | 46 |

| 13. Viewing the Design Memory Map                          | 48 |

| 14. Exporting Memory Map Report                            | 51 |

| 15. Exporting Interrupt Map Report                         | 53 |

| 16. Appendix A - Glossary                                  | 55 |

| 17. Appendix B - Available Cores in Libero SoC Catalog     | 56 |

| 18. Appendix C - Keyboard Shortcuts                        | 58 |

| 19. Appendix D – Component Types                           | 59 |

| 20. Appendix E – Operations Native to SmartDesign          | 61 |

| 21. Revision History                                       | 62 |

| Microchip FPGA Support                                     | 63 |

| Microchip Information                                      | 64 |

| Trademarks                                                 | 64 |

| Legal Notice                                               | 64 |

| Microchip Devices Code Protection Feature                  | 64 |

## 1. Understanding the SmartDesign Canvas (Ask a Question)

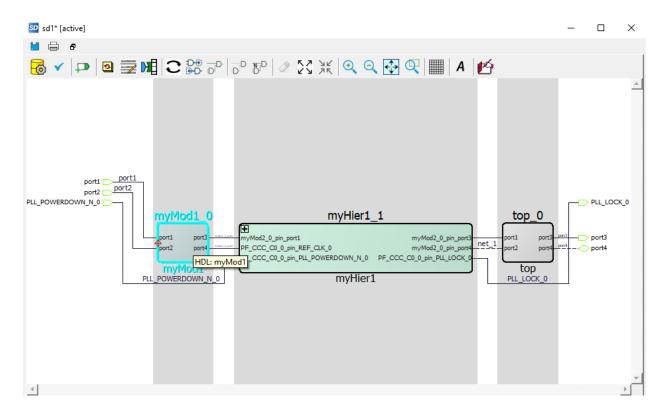

The SmartDesign canvas places all components in columns, with the nets vertically routed in the space between columns. Input ports are placed in the left-most column. Output ports and inout ports are placed in the right-most column. However, you can choose to move the ports or components to any location of your choice in the SmartDesign canvas.

When components are instantiated in the SmartDesign tool, they are either placed in an existing column or a new column is created for them. When you move the components vertically, you can see the column boundaries. You can also move the components horizontally to a new or an existing column.

The following figure shows the SmartDesign tool's canvas.

**Tip:** Click on specific area within the SmartDesign canvas image to know more about it.

Figure 1-1. SmartDesign Canvas at a Glimpse

## 1.1. Click and Drag Operations in the Canvas (Ask a Question)

The following table lists the mouse click and drag operations supported in the SmartDesign canvas.

Table 1-1. Click and Drag Operations in SmartDesign Canvas

| Operation | Action                                                               | Description                                                                                                                |

|-----------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Zoom in   | Click and drag the mouse pointer towards the top-left in the canvas. | The distance your cursor is dragged determines the magnitude of the zoom-in and is indicated by a positive integer in red. |

Table 1-1. Click and Drag Operations in SmartDesign Canvas (continued)

| Operation   | Action                                                                         | Description                                                                                                                 |

|-------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Zoom out    | Click and drag the mouse point towards the top-right in the canvas             | The distance your cursor is dragged determines the magnitude of the zoom-out and is indicated by a negative integer in red. |

| Zoom to fit | Click and drag the mouse pointer towards bottom-left in the canvas.            | Changes the display to tightly fit the design in the canvas.                                                                |

| Select      | Click and drag toward bottom-right in the canvas to select multiple instances. | Ensure that instances, pins, and ports you want select are fully contained inside the selection rectangle.                  |

To move the viewpoint/perspective of specific component(s) of your design to a specific area in the canvas, hold the **Ctrl** key down, drag and drop the components of the design to the required area in the canvas, and release the **Ctrl** key. Alternatively, you can perform this action by holding the mouse scroll wheel down and drag and drop the design to the required area in the canvas.

## 1.2. Additional Canvas Operations (Ask a Question)

The following table lists additional SmartDesign toolbar canvas operations. Hover your cursor over the icon to view the operation name in a tool tip. You can perform any of these operations by right-clicking in the empty space inside the canvas.

Table 1-2. Additional Toolbar Options

| Operation              | Action                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset Layout           | Resets the layout view using the built-in optimization algorithms                             | You can retain the presentation model (instance, port coordinates, and highlight colors) while saving your SmartDesign.  However, if you choose to clear the current presentation model, click on <b>Reset Layout</b> . This action removes all the presentation information (position, size, highlights, and modified pin orders) and recreates canvas layout using the built-in optimization algorithms. |

| Auto-arrange<br>Layout | Auto arranges the components in the layout using the built-in optimization algorithms         | Only the location (X-Y coordinates) of the instances and ports are changed. All presentation information remains intact.                                                                                                                                                                                                                                                                                   |

| Compress<br>Layout     | Compresses display of<br>the complete design using<br>the built-in optimization<br>algorithms | Click to push the instances and ports towards each other to remove the extra white space between them on the screen.  The relative positions of the instances on the screen are preserved. The result is a more compact display of the design.                                                                                                                                                             |

| Unhighlight All        | Removes all highlights in the design                                                          | Highlighting of all the design objects (nets, pins, ports, and instances) on<br>the canvas are removed.<br>This action is active only if design objects are already highlighted.                                                                                                                                                                                                                           |

| Zoom In                | Zooms in to the canvas                                                                        | Zoom in on the canvas.                                                                                                                                                                                                                                                                                                                                                                                     |

| Zoom Out               | Zooms out of the canvas                                                                       | Zoom out on the canvas.                                                                                                                                                                                                                                                                                                                                                                                    |

| Zoom to Fit            | Optimizes the design to the fit into the canvas                                               | Adjust the zoom and viewpoint, so that everything on the canvas fits within the visible view port with no extra empty space around the design.                                                                                                                                                                                                                                                             |

| Zoom to<br>Selection   | Zooms in to the selected area in the canvas                                                   | Click this action and drag the mouse to draw a rectangle which is when released, causes a zoom in, so that the visible view port area is approximately the size of the drawn rectangle.                                                                                                                                                                                                                    |

| Show Grid              | Makes the gridlines visible                                                                   | Click to show a background grid behind the items on the canvas. If the grid does not appear when the button is clicked, zoom in until the grid shows. The grid pattern might not show if the canvas is zoomed too far out.                                                                                                                                                                                 |

| Add Note               | Allows you to add notes in your design                                                        | Click to enter the <b>Add Note</b> mode.  During the next mouse click, the canvas opens a dialog box for entering the text and font size of the text (anchored at the mouse click location).                                                                                                                                                                                                               |

#### Table 1-2. Additional Toolbar Options (continued)

| Operation   | Action                           | Description                                                                                                                           |

|-------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Save to PDF | Saves the design to a .PDF file. | This action opens a dialog box that allows you to save a picture of all or part of the design to a $\mbox{.}\mbox{\tt PDF}$ document. |

## 2. Creating a Synthesizable SmartDesign (Ask a Question)

In the design process, the first step is to create a SmartDesign component after creating a project. Create your SmartDesign using the following procedures.

#### 2.1. Creating a SmartDesign Component (Ask a Question)

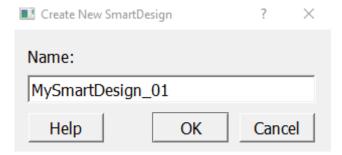

To create a SmartDesign component using the SmartDesign canvas, perform the following steps:

- 1. Launch the SmartDesign tool in either of the following ways.

- On the menu, click File > New > SmartDesign

- On the **Design Flow** tab, double-click **Create SmartDesign**

**Result:** The **Create New SmartDesign** dialog box appears.

Figure 2-1. Create New SmartDesign Dialog Box

- 2. Enter an appropriate and unique name for your SmartDesign component in the **Name** box.

- 3. Click **OK** to create the SmartDesign component. The SmartDesign component appears in the **Design Hierarchy** tab. The newly created SmartDesign appears as a central tab in the IDE main window.

**Result:** The design file is saved in a folder with the same name as that of the design itself and is placed in your project>\component\work\ folder.

## 2.2. Importing an Existing HDL Source File(s) or Folder(s) (Ask a Question)

To import an HDL design source file(s) or folder(s) use the following procedures.

- 1. Import your design sources in any of the following ways:

- On the menu, click File > Import and select HDL Source Files. The Import Files dialog box appears.

- On the menu, click File > Import, and select HDL Source Folder. The Import Folders dialog box appears.

- In the Design Flow tab, right-click on Create HDL option, and select Import Files. The Import Files dialog box appears.

- 2. Navigate to the location where your design source file(s) or folder(s) are located, select the file(s) or folder(s), and click **Open**.

**Result:** The selected file(s) or folder(s) are copied to your project>\hdl\ folder.

For more information, see Libero Design Flow User Guide.

## 2.3. Creating a New HDL File Using the IDE (Ask a Question)

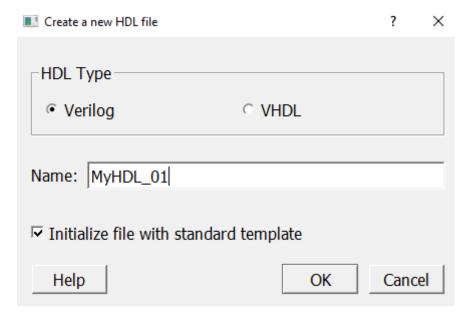

To create a new HDL file using the IDE, perform the following steps:

- 1. Launch the IDE in either of the following ways:

- On the menu, click **File** > **New** > **HDL**

- On the **Design Flow** tab, double-click **Create HDL**

**Result:** The **Create a new HDL file** dialog box appears.

Figure 2-2. Create new HDL file Dialog Box

- 2. By default, the preferred language to write the design file is set to **Verilog**. If you choose to use VHDL, select the **VHDL** option.

- 3. Enter an appropriate and unique name for your design file in the **Name** box.

- 4. By default, the design file is initialized with the built-in standard design file template. If you choose to not use the default template, deselect the **Initialize file with standard template** option.

- 5. Click **OK** to create the HDL file. The newly created HDL file appears in the **Design Hierarchy** tab and is displayed in the central tab of the IDE main window.

**Result:** The newly created HDL file is copied to your project>\hdl\ folder.

## 3. Instantiating User HDL Modules, IP Cores, and Components in SmartDesign (Aska Question)

You can add one or more HDL modules, building blocks, and components from the **Design Hierarchy** tab to your design. The components can be IP cores from the **IP Catalog** tab, basic macros, design blocks, and other SmartDesign components available from the **Components** node in the **Design Hierarchy** tree or from the **Components** tab.

#### 3.1. Instantiating a User HDL Module in your Design (Ask a Question)

To instantiate a user HDL source module, use either of the following procedures:

- On the **Design Hierarchy** tab, select the user HDL module of interest, drag and drop it onto the canvas.

- On the **Design Hierarchy** tab, right-click the user HDL module of interest and select **Instantiate** in **<active\_SD\_name>** from the right-click menu.

**Result:** The selected module is instantiated in the SmartDesign canvas.

**Tip:** Repeat these steps to instantiate all the user HDL source modules of interest in your SmartDesign canvas.

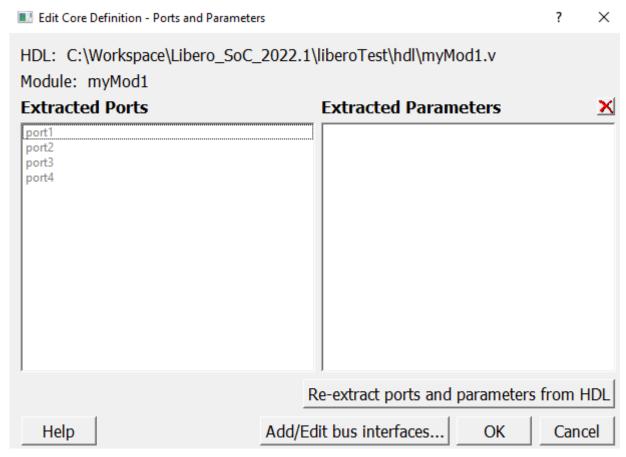

#### 3.2. Creating a HDL+ Core from an User HDL Source Module (Ask a Question)

To create a HDL+ core from a user HDL source module, perform the following steps:

On the **Design Hierarchy** tab, right-click the user HDL file and select **Create Core from HDL** from the right-click menu. The **Edit Core Definitions – Ports and Parameters** dialog box appears.

Figure 3-1. Edit Core Definitions – Ports and Parameters

2. Specify the ports and parameters as required and click **OK**. A BIF might also be added to the HDL core. It shows up in the SmartDesign with a BIF pin that can easily connect to the compatible instance BIF pins.

**Result:** The selected user HDL module is converted to an HDL+ core and can be instantiated in your SmartDesign canvas.

#### 3.3. Configuring and Instantiating Instances in your Design (Ask a Question)

You can choose to configure and instantiate the following components in your design:

- SmartDesign component

- IP Core components

- User HDL cores

- Design blocks

**Important:** Only IP core components can be configured.

#### 3.3.1. Configuring and Instantiating an IP Core Component (Ask a Question)

Microchip offers a large portfolio of configurable cores. These cores are available from the **Catalog** tab. To instantiate an IP core component in your design, you must first configure the component.

1. To configure and instantiate an IP core component, use either of the following procedures:

- On the Catalog tab, select the IP core component of interest, drag and drop it onto the canvas.

- On the **Catalog** tab, right-click the IP core component of interest and select **Instantiate in** <active\_SD\_name> from the right-click menu.

- On the **Catalog** tab, right-click the IP core component of interest and select **Configure core** from the right-click menu.

**Result:** The **Create Component** dialog box appears.

Figure 3-2. Create Component Dialog Box

By default, the selected IP core's name is displayed in the **Name** box. You can use the next step to change the core's name to a name of your choice.

2. Enter an appropriate and unique name for your core component in the **Name** box and click **OK**. The **Configurator** window appears.

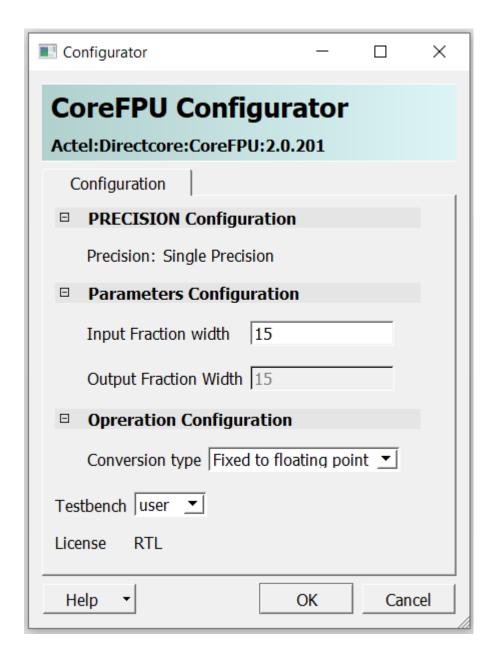

Figure 3-3. Configurator Window

- 3. Configure the core component as per your design requirements and click **OK**.

- 4. (Optional) To re-configure an existing component, right-click the component and choose **Configure**. The **Configurator** window appears. Proceed with step 3 to modify the existing configuration.

**Result**: The configured IP core component is made available in the **Design Hierarchy** tab, **Components** tab, and is instantiated in your SmartDesign canvas.

**Tip:** Repeat these steps to instantiate the necessary IP core components of interest in your SmartDesign.

**Important:** If you observe that the core component that you are looking for appears in italicized-gray color in the **Catalog** tab, it means that the core component is yet to be downloaded from the Microchip IP Core Repository to your hard disk (vault).

Download the core component of interest from the **Catalog** tab, in either of the following ways.

- Double-click the core component of interest.

- Right-click the core component of interest and click **Download**.

**Result:** The core component of interest is downloaded from the Microchip vault to your local vault and is made available for configuration and instantiation.

For information on the types of available core components and its color representation, see Appendix D – Component Types.

## 3.3.2. Instantiating SmartDesign Components, User HDL Cores, and Design Blocks in your Design (Ask a Question)

To instantiate a SmartDesign component, a user HDL core, or a design block use either of the following procedures:

- On the **Design Hierarchy** tab, select the SmartDesign component, user HDL core, or the design block of interest, drag, and drop it onto the canvas.

- On the **Design Hierarchy** tab, right-click the SmartDesign component, user HDL core, or the design block of interest, and select **Instantiate in <active\_SD\_name>** from the right-click menu.

**Result:** The selected components are instantiated in your SmartDesign.

#### Tip:

- Repeat these steps to include the necessary SmartDesign components, user HDL cores, or design blocks of interest in your design.

- A component is either created within the existing project or imported into the existing project. Once in the project, the method for instantiating a component in your SmartDesign is the same regardless of the component type.

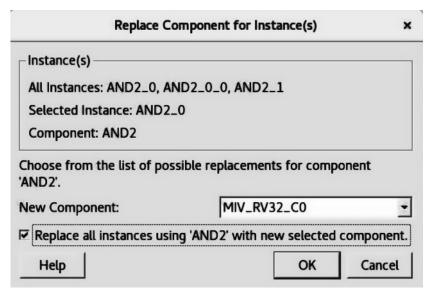

#### 3.4. Replacing an Instance Component with a Different Component (Ask a Question)

You can choose to replace an instance(s) component with a different component or a different implementation while preserving the current instance's interface (port) connections.

To replace an instance component with a different component, perform the following steps:

1. Right-click the instance component and select **Replace Component** from the right-click menu. The **Replace Component for Instance(s)** dialog box appears.

Figure 3-4. Replace Component for Instance(s) Dialog Box

The instance(s) section shows the following information:

- All Instances: Lists all instances of the component.

- Selected Instance: Shows the selected instance that will be replaced with the new component.

- **Component**: The component of the selected instance.

- 2. From the **New Component** dropdown list, select the replacement component of your choice.

- 3. By default, the **Replace all instances using <component\_name> with new selected component** option is selected. When this option is selected, every instance of the selected component in the current design (the list of instances shown under the **All Instances** group) are replaced with the new component specified in step 2.

#### Important:

- As a result of the replace action, if the instance port list changes, then some pins connections might be dropped. The information related to the dropped pins connection in printed in the **Log** window.

- If the Replace all instances using <component\_name> with new selected component option is deselected, only the selected instance is replaced in the design.

- If you select an instance and click **OK** for a non-valid component, the dialog box closes automatically, and an error message is printed in the **Log** window.

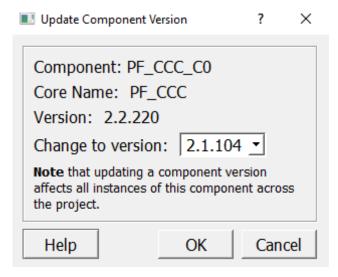

#### 3.5. Updating a Component Core Version (Ask a Question)

The **Update Component Version** functionality enables you to update a component of an instance with another version. You can restore or update your component without creating a new instance or losing your connections.

- 1. You can update a component version in your design in either of the following ways:

- On the **Design Hierarchy** tab, right-click the component and select **Update Component Version** from the right-click menu.

On the SmartDesign canvas, right-click the component and select **Update Component Version** from the right-click menu.

**Result:** The **Update Component Version** dialog box appears.

Figure 3-5. Update Component Version Dialog Box

2. The **Change to version** dropdown list contains all the versions of the selected core available in the vault. In the **Change to version** dropdown box, select the version you want to upgrade to and click **OK**.

**Result:** The core is automatically downloaded to the vault if it does not already exist in the vault. If the core exists in the vault, the component in the SmartDesign canvas is upgraded with the selected version.

**Important:** You cannot upgrade to a different version of the core that is not in your vault and if the vault is read-only.

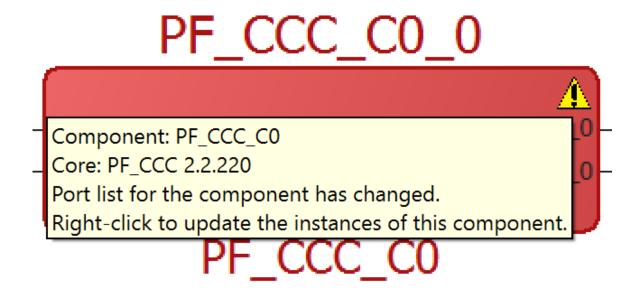

#### 3.6. Updating the Component Instance Port List (Ask a Question)

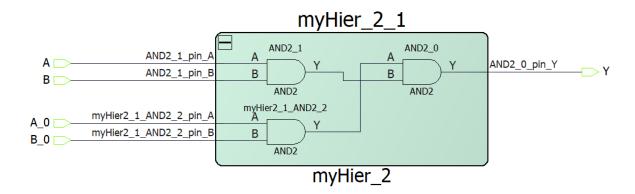

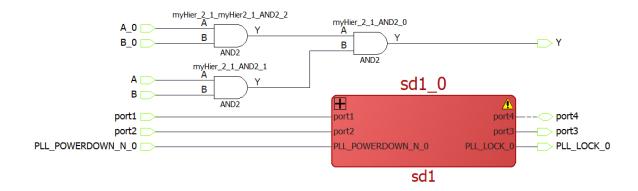

When the lower-level component port list is modified, the higher-level component is highlighted in red color and an exclamation symbol in shown within a red colored triangle at the top right corner of the component as shown in the following figure. This means that the instance port list needs to be updated.

Figure 3-6. Higher-level Component Highlighted in Red Color with Tooltip for User Action

Perform the following steps in the recommended order when the port list of the lower-level component is modified:

- 1. Go to the next higher-level of the design hierarchy containing lower-port modifications.

- 2. Right-click the lower-level component and select **Update Instance** from the right-click menu.

- 3. Generate the higher-level component in which the instance is updated.

**Result:**The red colored triangle at the top right corner of the component disappears if the component update is successful.

#### 3.7. Performing Additional Operations on Components (Ask a Question)

When one or more instances are selected, you can use the right-click menu to perform the following operations.

**Note:** Some operations are applicable only on a single instance.

Table 3-1. Performing Additional Operations on Components

| Operation  | Action                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configure  | If the selected instance is a configured core component or parametrized HDL core, the <b>Configure</b> option opens the <b>Configurator</b> dialog box for the core to be configured.  If the instance is a SmartDesign component, the <b>Configure</b> option brings up the SmartDesign canvas for edits.                                                                                                                                                   |

|            | If the selected instance is an HDL module, the <b>Configure</b> option brings up the HDL code editor to edit the instance module. The configure operation is equivalent to double-clicking the instance. The <b>Configure</b> option is available only when a single instance is selected.                                                                                                                                                                   |

|            | For more information, see Instantiating SmartDesign Components, User HDL Cores, and Design Blocks in your Design                                                                                                                                                                                                                                                                                                                                             |

| Modify HDL | The <b>Modify HDL</b> option brings up the HDL code editor to edit the HDL source file of the instance module. This option is available only when an instance of an HDL core is selected. <b>Note:</b> The <b>Modify HDL</b> option is only available for HDL modules. For an HDL module, double-click the HDL component in the SmartDesign canvas or right-click the HDL component and choose <b>Configure</b> to open the HDL file in the HDL code editor. |

| Table 3-1. Performing Additional Oper | ations on Components (continued) |

|---------------------------------------|----------------------------------|

|---------------------------------------|----------------------------------|

| Table 3-1. Felloll                                                   | Additional Operations on Components (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation                                                            | Action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Replace<br>Component                                                 | The <b>Replace Component</b> option allows you to replace an instance component with a different component or a different implementation while preserving the current instance's interface (port) connections.  For more information, see Replacing an Instance Component with a Different Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Update<br>Component<br>Version                                       | The <b>Update Component Version</b> option allows you to update a component of an instance with another version.  For more information, see <b>Updating a Component Core Version</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Rename                                                               | The <b>Rename</b> option prompts you to modify the selected instance name. Provide a new unique name for the instance and then click <b>OK</b> . <b>Note:</b> An error message is shown in the <b>Log</b> window if the instance name does not follow the HDL naming rules.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Delete                                                               | The <b>Delete</b> option deletes the selected item. When multiple items are selected, all of them are deleted. <b>Note:</b> Not all design objects can be deleted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

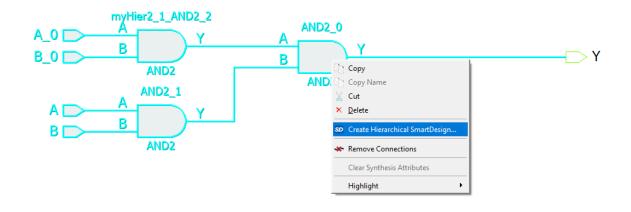

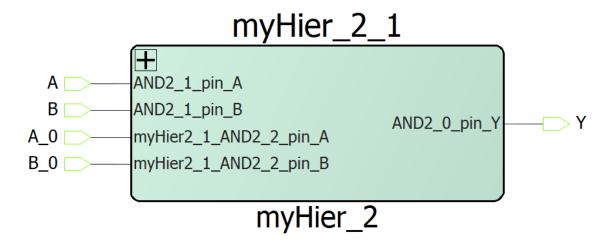

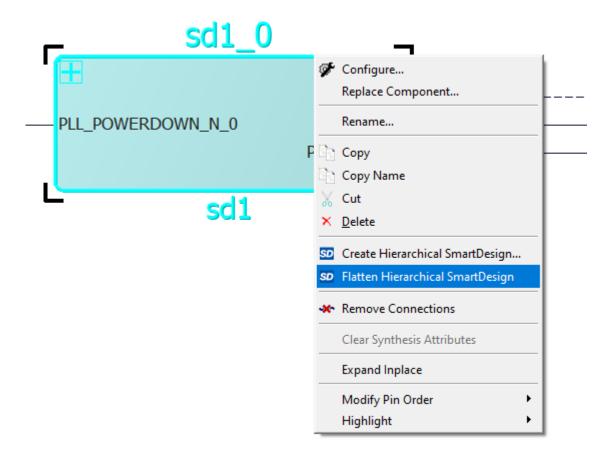

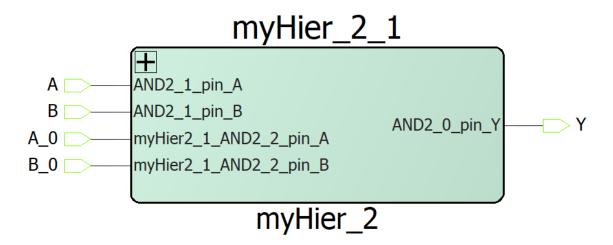

| Create Hierarchical SmartDesign and Flatten Hierarchical SmartDesign | You can choose to select one or more instances in your SmartDesign and create a new SmartDesign out of it (all the nets and connections from the instance are retained). or you can choose to flatten a hierarchical SmartDesign component.  For more information, see Working with Hierarchical SmartDesigns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Remove<br>Connections                                                | The <b>Remove Connections</b> option disconnects all pins that can be disconnected from nets. Pins that cannot be disconnected (for example, pins connected to pads) are logged in the <b>Log</b> window.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Highlight                                                            | The <b>Highlight</b> option opens a menu with multiple highlight color options. Select a color of your choice and the selected instances are highlighted with the chosen color. If any selected instances already have a different highlight, then such instances are highlighted with the chosen new color. This option is available when a single or multiple instances, nets, or ports are selected. If you highlight an instance, it automatically highlights the non-highlighted pins of the instance. Click <b>Unhighlight all</b> in the SmartDesign toolbar to remove the highlight color of all highlighted design objects, including highlighted nets. The <b>Highlight</b> option is also available in the right-click menu of the low-level instances in the <b>Expanded Inplace</b> view. |

| Help                                                                 | This option brings up the handbook, the release notes, or the configuration user guides for the core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

# 4. Creating Pins and Ports for Connecting Instances in the SmartDesign (Aska Question)

After placing the components in your SmartDesign canvas, you now need to create pins and ports to connect the various instances to complete your design.

Each pin or port has a direction and a type. Direction of the regular ports (non-Bus Interface ports) can be input, output, and bidirectional (inout).

The following is a list of types of pins or ports:

- Scalar: Single unit-level signal

- **Bus**: Array of scalar ports. The range of the bus ports are indicated by square brackets [nFirst:nLast]. For Example, busName[3:0].

- Slice: Slice is a part of a bus port. A bus slice is of any range size within the bus range. For example, sliceName[0], sliceName[2:0].

- **Bus Interface (BIF)**: A Bus Interface is a bundle of scalar or bus ports that has functional meaning to it. BIF ports have characteristics such as functional types and roles that define how two Bus Interfaces can connect to one another. SmartDesign provides a rich set of AMBA Bus Interfaces—AXI, AXI4, AXI4Stream, AHB, AHBLite, and APB3 to help create easily AMBA sub-systems. It also provides Microchip specific Bus Interface types for easy connectivity between Microchip hardware components.

Scalar ports or pins in SmartDesign may have a PAD characteristic property. A pin or port with a PAD property must be connected to a top-level port of the design. PAD ports eventually assign to a package pin. In SmartDesign, these ports are automatically promoted to the top-level and can be modified, if needed.

For better organization of the instance pins, you can create groups. Groups are displayed on an instance with a Group pin that is just a visual representation and cannot be connected. Any pin can be added or removed from the group. Groups can be collapsed to hide member pins.

#### 4.1. Creating Pins and Ports for your Design (Ask a Question)

After placing the components in your SmartDesign canvas, you now need to create pins and ports to connect the various instances to complete your design.

Each pin or port has a direction and a type. Direction of the regular ports (non-Bus Interface ports) can be input, output, and bidirectional (inout).

- 1. You can create a pin or port in either of the following ways:

- On the menu, click SmartDesign > Add Port

- On the SmartDesign toolbar, click Add Port

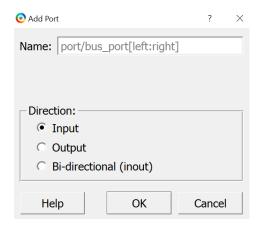

**Result:** The **Add Port** dialog appears.

Figure 4-1. Add Port Dialog

- 2. Enter an appropriate and unique name for the port in the **Name** box. You can specify a bus port by indicating the bus range directly into the name using brackets []. For example, mybus [3:0].

- Important: If the port name violates HDL naming rules, an error message is printed in the **Log** window, and the new port is not created.

- 3. Choose the pin or port type that you want to create as per the following table and then click **OK**. The chosen port type is created in the SmartDesign canvas.

Table 4-1. Pin and Port Type Description

| Pin or Port Type       | Representation | Purpose                                                                                                                                                           |

|------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input                  | - Unconnected  | Input port for operating with inputs. By default, the input pins and ports are placed on the left side of the canvas.                                             |

| Output                 | - Unconnected  | Output port for operating with outputs. By default, the output pins and ports are placed on the right side of the canvas.                                         |

| Bi-directional (inout) | - Unconnected  | Bi-directional port for operating as an input or an output pin or port. By default, the bi-directional pins and ports are placed on the right side of the canvas. |

**Tip:** To remove a port from the top-level, right-click the port, and select **Delete** from the right-click menu or select the port and press the **Delete** key.

#### 4.2. Modifying the Pin Order (Ask a Question)

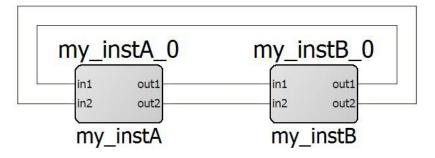

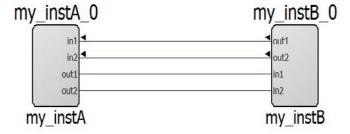

If the outputs of one component (instance A) communicate with the inputs of another component (instance B) and otherwise, nets may intersect with each other and the view may be cluttered. To prevent this, the **Modify Pin Order** functionality allows you to modify the default pin placement of the instance.

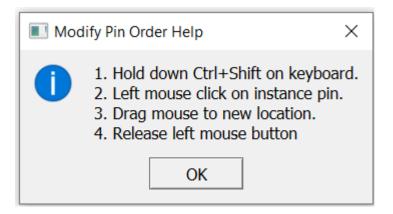

To modify the default pin placement of the instance:

1. Right-click the component and select **Modify Pin Order** > **Modify Pin Order** from the right-click menu. The **Modify Pin Order Help** dialog box appears.

Figure 4-2. Modify Pin Order Help Dialog Box

2. Follow the instructions in **Modify Pin Order Help** dialog box to move the pin.

A pin that has been moved away from default locations is identified by a bold arrowhead. An inward-pointing arrowhead indicates an input pin and an outward-pointing arrowhead indicates an output pin. Inout pins do not have an arrowhead when they are moved away from the default locations (right side of instance).

Figure 4-3. Connections Between Two Instances with Regular Pin Order

Figure 4-4. Connections Between Two Instances with Modified Pin Order

3. To reset the instance pin order to its default order, right-click the instance, and select **Modify Pin Order** > **Reset Pin Order** from the right-click menu.

**Important:** The **Modify Pin Order** operation is unavailable when the instance is expanded in place. The modified pin order might not be preserved when an instance is expanded but retains the set order when folded.

## 4.3. Performing Operations on Pins or Ports (Ask a Question)

When one or more pins or ports are selected, you can use the right-click menu to perform the following operations on the ports and pins.

Table 4-2. Possible Operations on Pins and Ports

| 14510 7 2.1 0331                                                                                                                                                                                                                                                                                                                  | ble operations on rins and rolts                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Operation                                                                                                                                                                                                                                                                                                                         | Action                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Connect                                                                                                                                                                                                                                                                                                                           | The <b>Connect</b> command connects the selected pins and ports with a net. If there is a net selected, it is used to make the connection. This is the only pin or port action that takes selected nets into account. If the connection is not possible, an error message is printed in the <b>Log</b> window. A connection is established only if all the selected objects can be connected.                         |  |  |

| Disconnect                                                                                                                                                                                                                                                                                                                        | The <b>Disconnect</b> command disconnects all the selected non-pad pins or ports from their attached net.                                                                                                                                                                                                                                                                                                             |  |  |

| Promote to<br>Top-Level                                                                                                                                                                                                                                                                                                           | The <b>Promote to Top-Level</b> command is available to all non-PAD pins. It creates a port and a net connecting the port to the pins or slices. If a port with the same name already exists, a new unique port name is created.  For example, if a BIF (myBIF) pin contains a pin (myPort), then the top-level myPort is named myBIF myPort after the myBIF pin is promoted to the top level.                        |  |  |

| Go to Driver                                                                                                                                                                                                                                                                                                                      | The <b>Go to Driver</b> command zooms onto the driver of the selected pin or port. The <b>Go to Driver</b> command is not available for output pins and input ports. The driver cannot be an inout.                                                                                                                                                                                                                   |  |  |

| Magnify Pin                                                                                                                                                                                                                                                                                                                       | Double-click a pin/port or right-click and select <b>Magnify Pin</b> to zoom into the pin/port connection. The <b>Magnify Pin</b> window shows the specified pin/port connections. If the pin has a fanout of more than one, the number beside the + sign on the right shows the total fanout count.  Click the + sign to see all the fanouts of the pin. You can double-click the net, pin, port, or instance inside |  |  |

|                                                                                                                                                                                                                                                                                                                                   | the <b>Magnify</b> window to zoom and select the item.                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Modify/<br>Rename                                                                                                                                                                                                                                                                                                                 | The <b>Modify</b> or <b>Rename</b> command opens a <b>Modify Port</b> dialog box. You can change the port name and the range of the port. <b>Notes:</b> • All slices of the bus are deleted if the range is changed.  • When renaming BIF port, all the member ports that have BIF name prefix are renamed.                                                                                                           |  |  |

| Delete                                                                                                                                                                                                                                                                                                                            | , ,                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| The <b>Delete</b> Command deletes all the selected items that can be deleted: slices, user created a members, and ports.  The <b>Delete</b> command deletes all the selected items, even if the selected items are of different When a group member is deleted, the member is deleted from the group only. The actual pindeleted. |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Mark Unused                                                                                                                                                                                                                                                                                                                       | This option is available to the output pins (scalar, bus, and BIF) of an instance. The <b>Mark Unused</b> command allows you to show the output pins that are not being used in the design and must not be flagged as a warning when generating the design or running the DRC operation.                                                                                                                              |  |  |

| Invert                                                                                                                                                                                                                                                                                                                            | The <b>Invert</b> command inverts the input or output scalar pin and port. A bubble is added to indicate inversion.                                                                                                                                                                                                                                                                                                   |  |  |

| Tie High                                                                                                                                                                                                                                                                                                                          | The <b>Tie High</b> command connects the pin (scalar and bus) to a logical 1. For a bus pin, this action delete slices. For a group, this action is applied to all non-output member pins in the group.                                                                                                                                                                                                               |  |  |

| <b>Tie Low</b> The <b>Tie Low</b> command connects the pin (scalar and bus) to a logical 0. For a bus pin, this action slices. For a group, this action is applied to all non-output member pins in the group.                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Tie Constant                                                                                                                                                                                                                                                                                                                      | The <b>Tie Constant</b> command is available only to bus pins and slices (except single-bit slice). It opens the Tie to Constant dialog box for a constant value in HEX to be entered for the bus pins and slices.                                                                                                                                                                                                    |  |  |

| Clear<br>Attributes                                                                                                                                                                                                                                                                                                               | The <b>Clear Attributes</b> command clears the pin attributes (Tie to High, Low, Constant, Inversion, or Marked Unused).                                                                                                                                                                                                                                                                                              |  |  |

|                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Table 4-2. Possible Operations on Pins and Ports (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Operation                                                    | Action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Highlight                                                    | The <b>Highlight</b> option opens a menu with multiple highlight color selections. Select a color to highlight the selected items. If any items are already highlighted, then choosing a different color highlight changes from the previous highlight color. This option is available when a single or multiple instances, nets, and ports are selected.  If you highlight an instance, it automatically highlights the non-highlighted pins of the instance. Click the <b>Unhighlight all</b> icon ( ) in the toolbar to remove the highlight color of all highlighted design objects, including highlighted nets. The <b>Highlight</b> option is also available in the right-click menu of the low-level instances in the <b>Expanded Inplace</b> view. |  |

| <b>Bus and Slice</b> operations                              | When a bus, slice pins, or ports are selected, the right-click menu in addition to regular pin actions have additional commands. For more information, see Working with Bus and Slice.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Add Pin to New<br>Group and Add<br>Pin to Group              | d Add Pin to Group to add the pin to the selected group. If no group is selected, the Add Pin to New Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Rename<br>(Group)                                            | Group pins, unlike other instance pins, can also be renamed. Right-click <b>Group</b> and choose <b>Rename</b> . The <b>Rename Group</b> dialog box appears. You can choose to change the name of the group in this dialog box and click <b>OK</b> to apply the changes.  If an invalid name is entered or a pin with that name already exists, then an error message is printed in the <b>Log</b> window.                                                                                                                                                                                                                                                                                                                                                 |  |

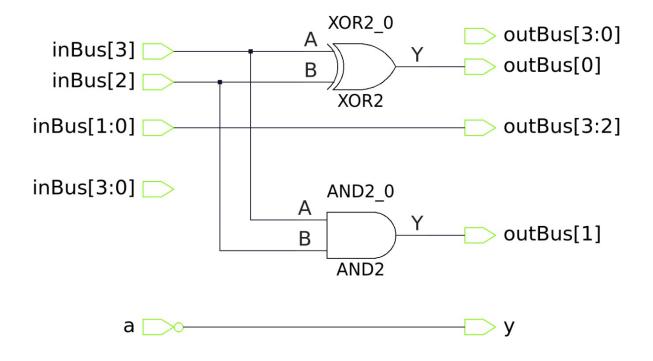

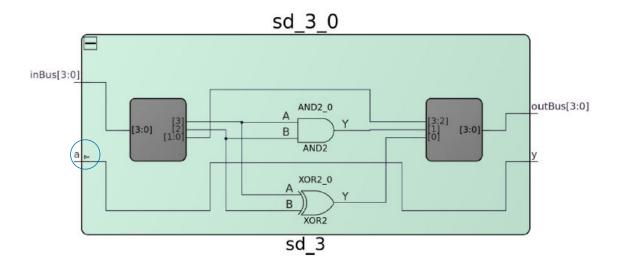

#### 4.4. Working with Bus and Slice (Ask a Question)

Table 4-2. Possible Operations on Pins and Ports (continued)

You can perform the following operations on a Bus or Slice using the right-click menu options:

- Flip Bit Order: This command is available only for slices. This option allows you to flip the slice range. For example, mySlice[10:0] is flipped to mySlice[0:10] of the slice. All connection or tieoff information and presentation information is retained.

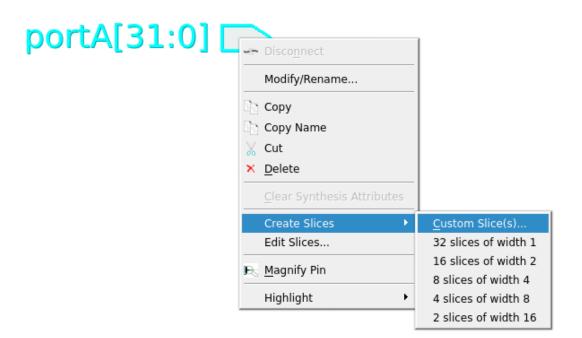

- **Create Slice**: This command opens a menu of slice options that can be created from the bus pin or ports. The custom slice(s) option can be used to create any slice or bit combination of your choice. For example, using a 32-bit bus with the Custom Slices option allows you to create any slice or bit combinations (For example, a slice of 10 bits and another slice of 22 bits). To make it convenient to create slices, common slice ranges for the selected bus are listed in the list. For example,

- 32 slices of width 1

- 16 slices of width 2

- 8 slices of width 4

- 4 slices of width 8

- 2 slices of width 16

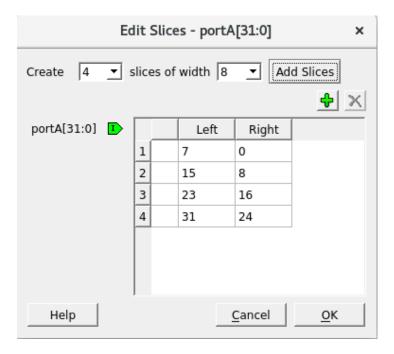

Figure 4-5. Slice Creation for a 32-Bit Bus

The directions of the slices (input or output) are indicated by an arrowhead and match the bus pin or port direction. On a bus port, the slices are placed in a column behind the bus port.

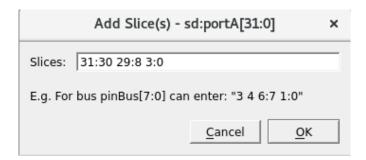

• Custom Slices: This command opens the Add Slice(s) dialog box for entering a list of slices.

Figure 4-6. Add Slices Dialog Box

If these slices are all valid, they are added to the bus. If the slices are not valid (For example, out-of-range slices, overlapping slices for input pins (output ports), or existing slices), the error is printed in the **Log** window. The dialog box supports any separator character except colon because the colon is used to specify a range. No characters other than the colon are allowed to be adjacent to the two-range indices.

**Tip:** Creating a **Custom Slice** does not delete any pre-existing slices.

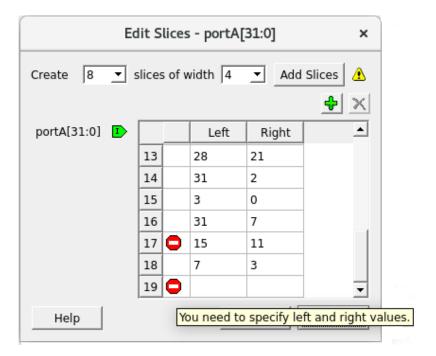

• **Edit Slice**: This command opens the **Edit Slices** dialog box. You can choose to delete, modify, and create a new slice, if required.

Figure 4-7. Edit Slices Dialog Box

Use the dialog box to change the range of the bits, add a slice, or delete a slice. If you specify invalid range values, an error icon appears in the **Edit Slices** dialog box. Hover your cursor over the error icon to display the error message.

Figure 4-8. Edit Slices - Tooltip and Error Message

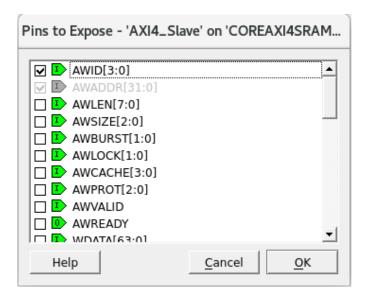

• Pins to Expose: This command opens the Pins to Expose dialog box displaying all the Bus Interface pins that can be exposed or hidden.

Figure 4-9. Pins to Expose Dialog Box

In the dialog box, you can check the pins in the BIF that you want to expose and deselect the ones that you want to be hidden. Hidden BIF pins are not visible in the SmartDesign canvas.

**Important:** Not all pins can be exposed. If a BIF pin is already connected, none of the input pins can be exposed. If a BIF pin is not connected, every item in the menu can be exposed.

## 5. Connecting Instances in your SmartDesign (Ask a Question)

In a SmartDesign, pins and ports are connected by nets. You can create manual connections between pins of the instances and ports in your design using the canvas.

Unused input scalar pins and output ports are set to high (1) or low (0). Unused input bus pins and output ports are set to a constant. Unused output pins and input ports are left unconnected when marked as unused.

**Important:** The nets that connect PAD pins and ports are called PAD nets. Such PAD nets cannot be deleted.

For more information one pins and ports, see .Creating Pins and Ports for Connecting Instances in the SmartDesign

To connect instances in your design, use either of the following methods.

#### 5.1. Method 1: Using the Drag and Drop Feature (Ask a Question)

Hovering your cursor over a pin or port activates the connection mode automatically and the cursor changes to a crosshair. Click and drag the mouse pointer to the target pin or port and release the mouse button to make the connection.

- For pins, the connection mode activates when you hover over a pin icon or a pin name.

- For nets, the connections mode activates when you hover over any part of the net.

- The connection mode does not activate when you hover over pins, ports, or nets in the following cases:

- When in a hierarchical view

- When **Zoom to Selected Area** mode is activated

- When **Add Note** mode is activated

- When the canvas is in a read-only **Filtered** mode

## 5.2. Method 2: Using the Right-click Menu (Ask a Question)

You can also connect multiple pins or ports through the right-click menu options.

To connect the selected pins, perform the following steps:

- 1. Select a pin

- 2. Press the **Ctrl** key and select the required pins

- 3. Right-click on any of the selected pins and click **Connect**

**Note:** The **Connect** menu option is enabled only if the connection operation between the selected pins is logically feasible.

## 5.3. Showing or Hiding Nets and Net Names (Ask a Question)

You can choose to show or hide nets and net names on the canvas.

To show or hide nets, click **Show or Hide Net** toggle icon in the SmartDesign toolbar. When a net is hidden, the net stubs that the hidden net is connected to are still visible. Selecting the net stubs shows the RATS net connection of the net.

To show or hide net names, click **Show or Hide Net Names** toggle icon in the SmartDesign toolbar. The net names are displayed alongside the net. Hiding net names makes the canvas less cluttered for big designs.

**Tip:** Net names always display in a tooltip when the cursor is hovered over the net.

## 5.4. Performing Operations on Nets (Ask a Question)

When a net or multiple nets are selected, the following commands are available in the right-click menu.

| Operation    | Action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connect      | The <b>Connect</b> command combines all the selected pins or ports to form a connection. Selecting a net is functionally equivalent to selecting all pins and ports that this net is connected to. Therefore, if you connect a net and a pin, it is equivalent to connecting all pins/ports of the net and the newly selected pin/port. The <b>Connect</b> command can also be used to connect a net to another net if one of the nets is not driven.                                                                                                                                                                                                               |

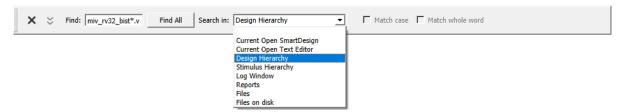

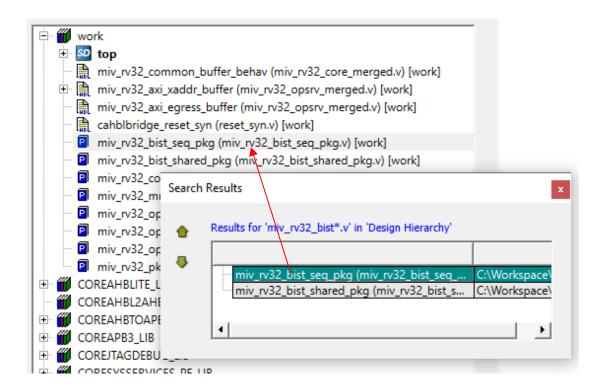

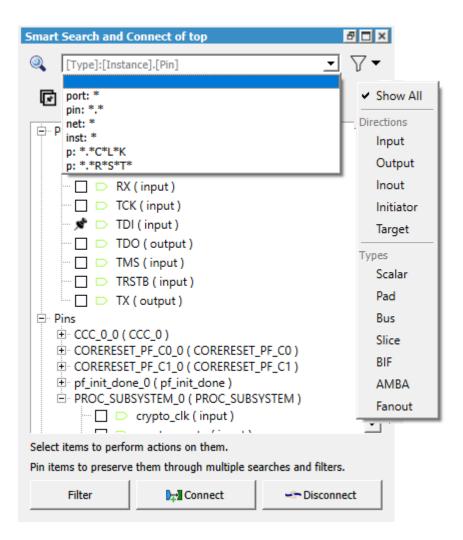

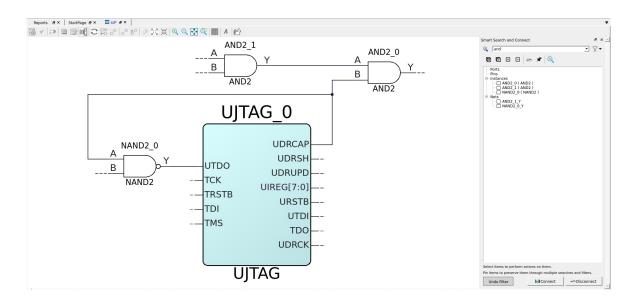

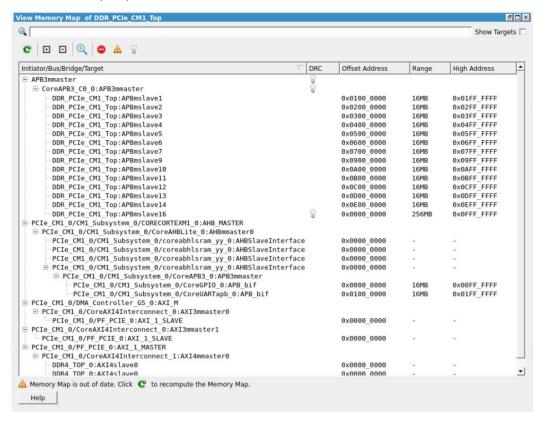

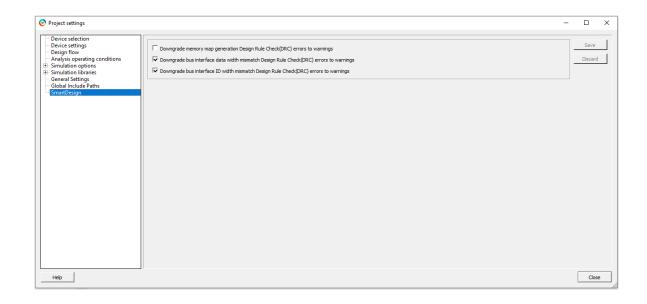

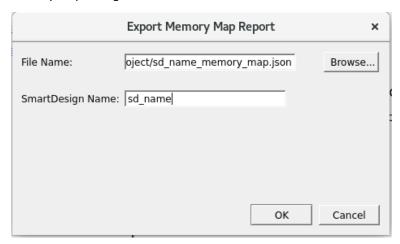

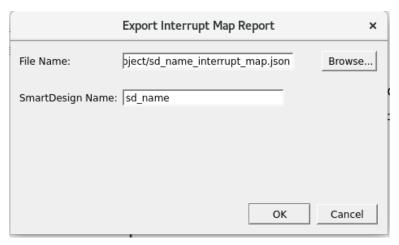

| Go to Driver | When a net is selected, the <b>Go to Driver</b> command centers the view on the net's driver pin or port, zooms away, and selects the net driver. <b>Go to Driver</b> traces the net to the driver at the local level of hierarchy. It does not traverse hierarchy. The <b>Go to Driver</b> command is not available when multiple nets are selected, or the selected net has no driver. In the latter case, the net displays as a dotted line.                                                                                                                                                                                                                     |