# Classic Constraint Flow User Guide

Libero SoC v11.8 SP1, SP2, and SP3

NOTE: PDF files are intended to be viewed on the printed page; links and cross-references in this PDF file may point to external files and generate an error when clicked. **View the online help included with software to enable all linked content.**

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email:

sales.support@microsemi.com www.microsemi.com

©2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

5-02-9120-38/07.17

# **Table of Contents**

| Table of Contents                                   | 4  |

|-----------------------------------------------------|----|

| Libero SoC Introduction                             | 12 |

| Welcome to Microsemi's Libero® SoC v11.8 SP1        |    |

| Libero SoC Design Flow (Classic Constraint Flow)    |    |

| Microsemi License Utility                           |    |

| File Types in Libero SoC                            |    |

| Software Tools - Libero SoC                         |    |

| Frequently Asked Questions - Libero SoC             |    |

| Firmware Cores Frequently Asked Questions           |    |

| Software IDE Integration                            |    |

| Running Libero SoC from your Software Tool Chain    |    |

|                                                     |    |

| Create Design                                       |    |

| System Builder                                      |    |

| Instantiate a SmartFusion MSS in your Design        |    |

| Configure the SmartFusion MSS                       |    |

| Generate SmartFusion MSS Files.                     |    |

| Instantiate a SmartFusion2 MSS in your Design       |    |

| Configure the SmartFusion2 MSS                      |    |

| Generate SmartFusion2 MSS Files                     |    |

| About SmartDesign                                   |    |

| SmartDesign Design Flow                             |    |

| Using Existing Projects with SmartDesign            |    |

| SmartDesign Frequently Asked Questions              |    |

| General Questions                                   |    |

| Instantiating Into Your SmartDesign                 |    |

| Working in SmartDesign                              |    |

| Working with Processor-Based Designs in SmartDesign |    |

| VHDL Construct Support in SmartDesign               |    |

| Making your Design Look Nice                        |    |

| Generating your Design                              |    |

| Creating a New SmartDesign Component                |    |

| Opening an Existing SmartDesign Component           |    |

| Saving/Closing a SmartDesign Component              |    |

| Generating a SmartDesign Component                  | 33 |

| Importing a SmartDesign Component                               | 34 |

|-----------------------------------------------------------------|----|

| Deleting a SmartDesign Component from the Libero SoC Project    | 34 |

| Generating a Memory Map                                         | 34 |

| Modify Memory Map Dialog Box                                    | 37 |

| Canvas Overview                                                 | 38 |

| Displaying Connections on the Canvas                            | 40 |

| Making Connections Using the Canvas                             | 42 |

| Simplifying the Display of Pins on an Instance using Pin Groups | 43 |

| Bus Instances                                                   | 44 |

| Adding Graphic Objects                                          | 44 |

| Auto-Arranging Instances                                        |    |

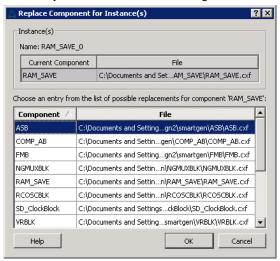

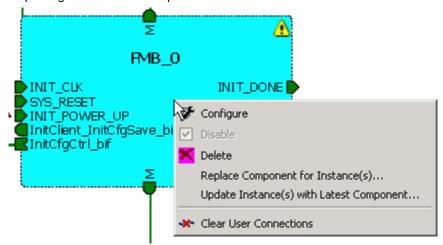

| Replace Component for Instance                                  |    |

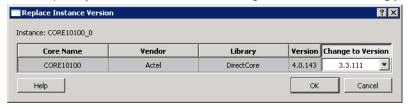

| Replace Instance Version                                        |    |

| Slicing                                                         |    |

| Rename Net                                                      |    |

| Organizing Your Design on the Canvas                            |    |

| Renaming a Component                                            |    |

| Adding Components and Modules (Instantiating)                   |    |

| Adding or Modifying Top Level Ports                             |    |

| Automatic Connections                                           |    |

| QuickConnect                                                    |    |

| Manual Connections                                              |    |

| Deleting Connections                                            |    |

| Top-Level Connections                                           |    |

| About Bus Interfaces                                            |    |

| Using Bus Interfaces in SmartDesign                             |    |

| Adding or Modifying Bus Interfaces in SmartDesign               |    |

| Bus Interfaces                                                  |    |

| DirectCore Bus Interfaces                                       |    |

| Show/Hide Bus Interface Pins                                    |    |

| Default Tie-offs with Bus Interfaces                            |    |

|                                                                 |    |

| Tying Off (Disabling) Unused Bus Interfaces                     |    |

| Required vs. Optional Bus Interfaces                            |    |

| Promoting Bus Interfaces to Top-level                           |    |

| Reconfiguring a Component                                       |    |

| Fixing an Out-of-Date Instance                                  |    |

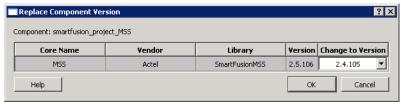

| Replacing Component Version                                     |    |

| Design State Management                                         |    |

| Design Rules Check                                              |    |

| Generating a SmartDesign Component                              |    |

| SmartDesign Menu                                                |    |

| SmartDesign Glossary                                            |    |

| Canvas Icons                                                    |    |

| VHDL Special Types - Examples and meta.out File Format          |    |

| Create Core from HDL                                            |    |

| Create HDI                                                      | 80 |

| Using the HDL Editor                                                     | 80  |

|--------------------------------------------------------------------------|-----|

| Importing HDL Source Files                                               |     |

| Mixed-HDL Support in Libero SoC                                          |     |

| SmartDesign Testbench                                                    |     |

| HDL Testbench                                                            | 82  |

| View/Configure Firmware Cores                                            |     |

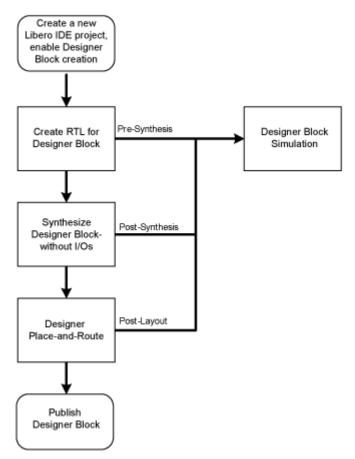

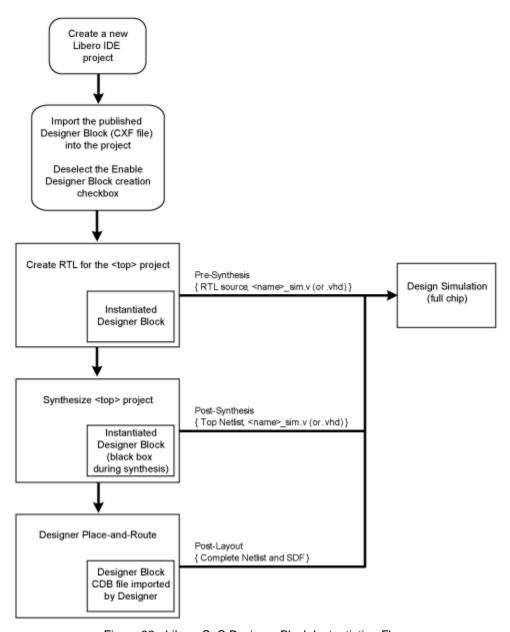

| Designing with Designer Block Components                                 | 86  |

| Designer Blocks and Synthesis                                            | 87  |

| Managing I/Os in a Designer Block Component                              | 88  |

| Globals and Designer Block Components                                    |     |

| Designer Block Compile Report                                            | 88  |

| Designer Block Component Limitations                                     |     |

| Creating a Designer Block Component in Libero SoC                        |     |

| Instantiating a Designer Block in Libero SoC                             |     |

| RTL Simulation                                                           |     |

| Simulation Options                                                       | 92  |

| Selecting a Stimulus File for Simulation                                 | 94  |

| Selecting Additional Modules for Simulation                              |     |

| Performing Functional Simulation                                         | 94  |

| Performing DirectCore Functional Simulation                              |     |

|                                                                          |     |

| Create Constraints                                                       | 96  |

| Constraints Overview                                                     | 96  |

| I/O Constraints - SmartFusion2, IGLOO2, RTG4                             | 96  |

| Timing Constraints - SmartFusion2, IGLOO2, and RTG4                      | 97  |

| Floorplan Constraints - SmartFusion2, IGLOO2, RTG4                       | 98  |

|                                                                          |     |

| Implement Design                                                         |     |

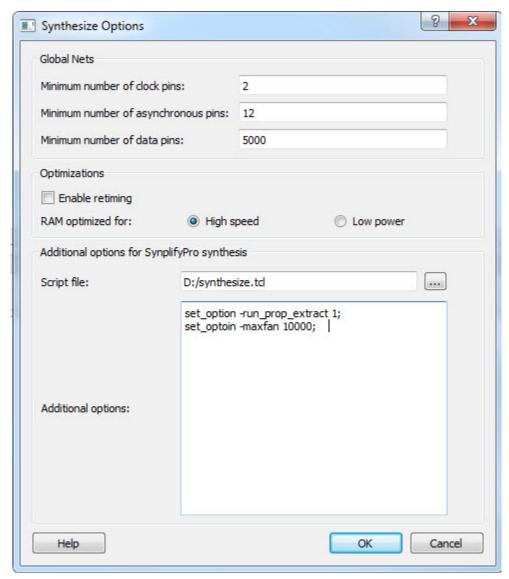

| Synthesize (Classic Constraint Flow)                                     |     |

| Synplify Pro ME                                                          |     |

| Precision RTL                                                            |     |

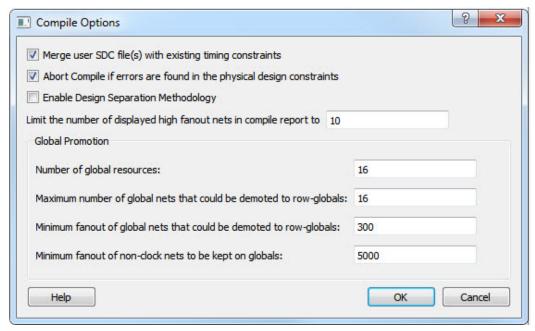

| Compile - SmartFusion, IGLOO, ProASIC3, Fusion                           |     |

| Compile - SmartFusion2, IGLOO2, and RTG4                                 |     |

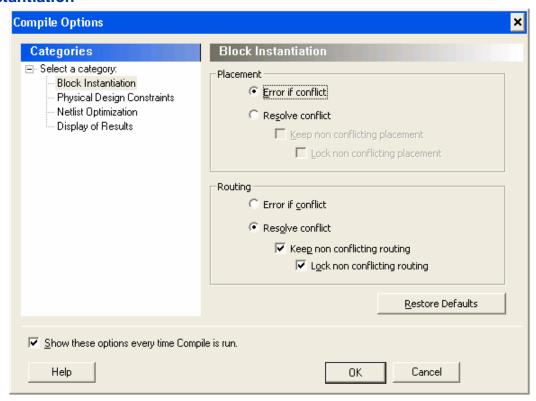

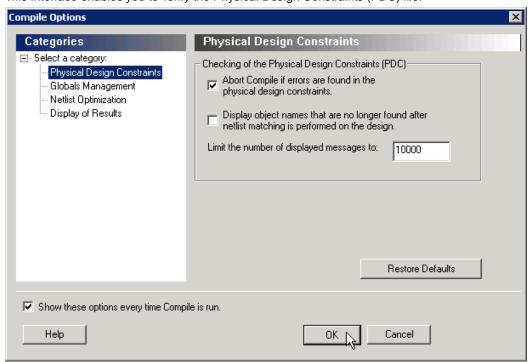

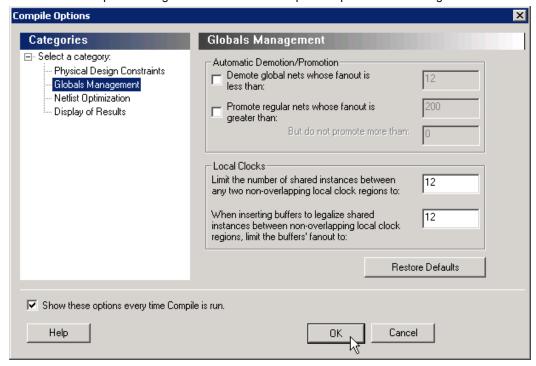

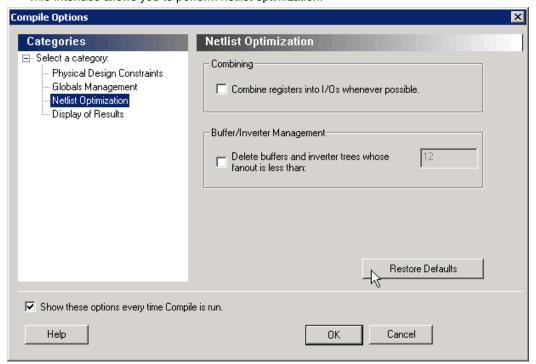

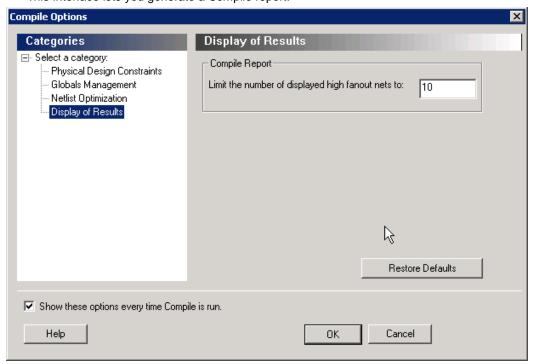

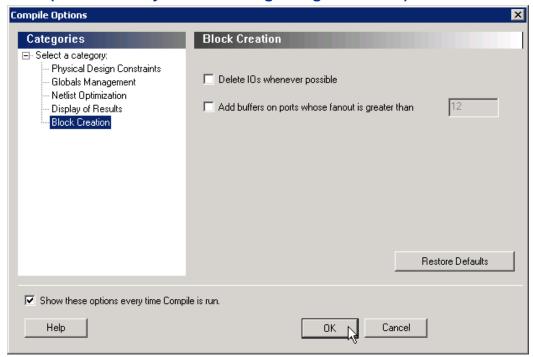

| Compile Options (SmartFusion, IGLOO, ProASIC3, and Fusion)               |     |

| Configure Flash*Freeze                                                   |     |

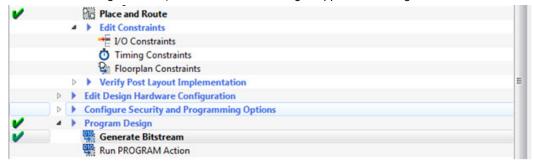

| Place and Route - SmartFusion2, IGLOO2, RTG4                             |     |

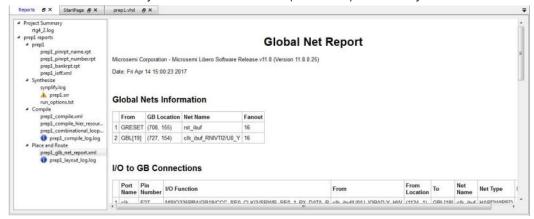

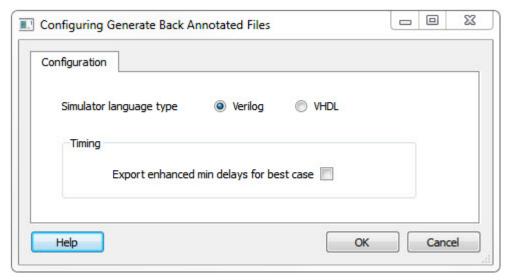

| Global Net Report                                                        |     |

| Place and Route                                                          |     |

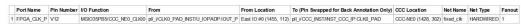

| Multiple Pass Layout Configuration (SmartFusion2, IGLOO2, RTG4)          |     |

| SmartFusion, IGLOO, ProASIC3 and Fusion Place and Route Advanced Options |     |

| Simulate - Opens ModelSim ME                                             |     |

| Generate Back Annotated Files - SmartFusion2, IGLOO2, and RTG4           |     |

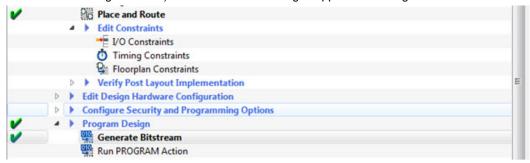

| Generate Bitstream                                                       |     |

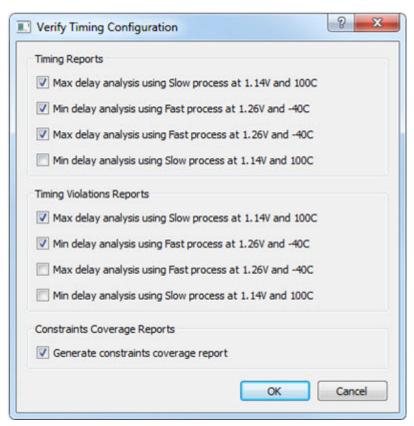

| Verify Timing Configuration                                              | 132 |

| Types of Timing Reports                                                           | 134         |

|-----------------------------------------------------------------------------------|-------------|

| Verify Timing with SmartTime                                                      | 136         |

| Verify Power with SmartPower                                                      | 136         |

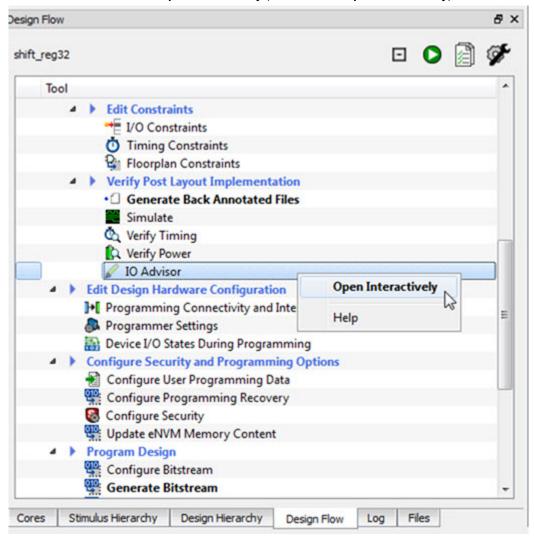

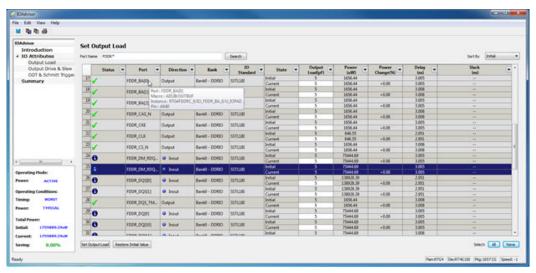

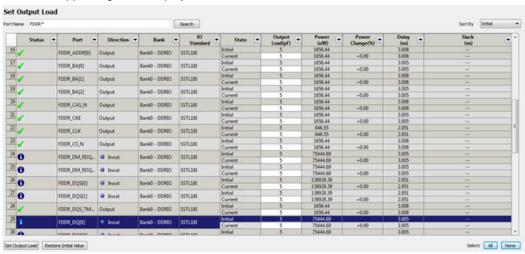

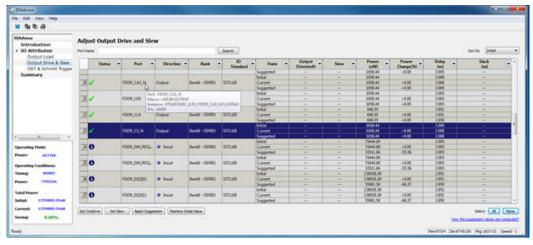

| IO Advisor (SmartFusion2, IGLOO2, and RTG4)                                       | 137         |

| Simultaneous Switching Noise                                                      |             |

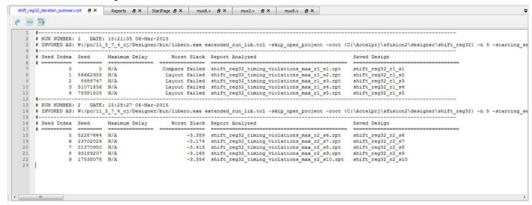

| Generate Back Annotated Files - SmartFusion2, IGLOO2, and RTG4                    | 150         |

| Device Programming                                                                | 152         |

| Programming Connectivity and Interface                                            | 153         |

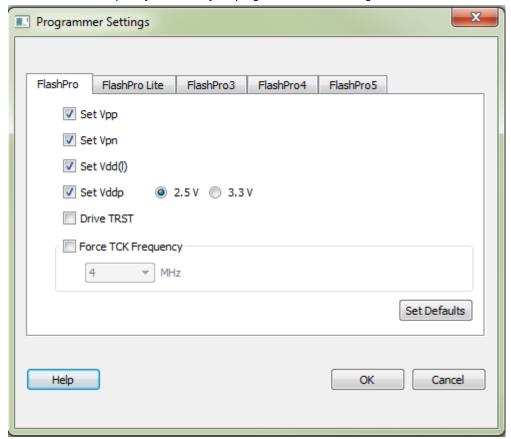

| Programmer Settings                                                               | 155         |

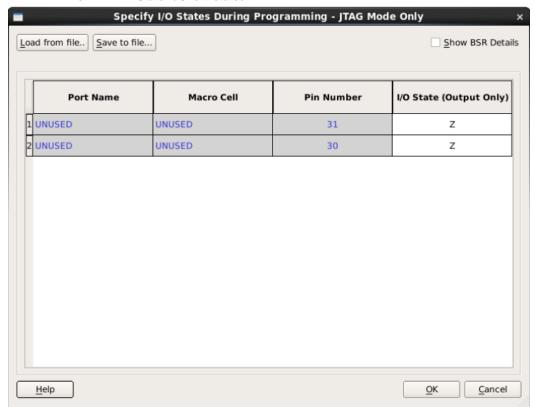

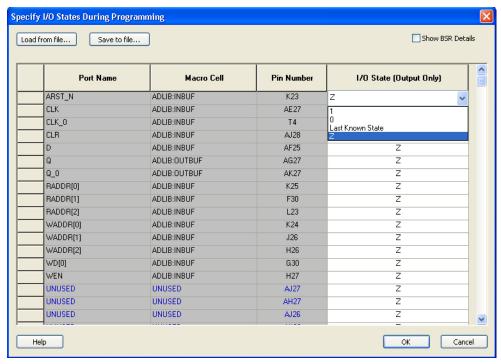

| Device I/O States During Programming JTAG Mode Only                               | 158         |

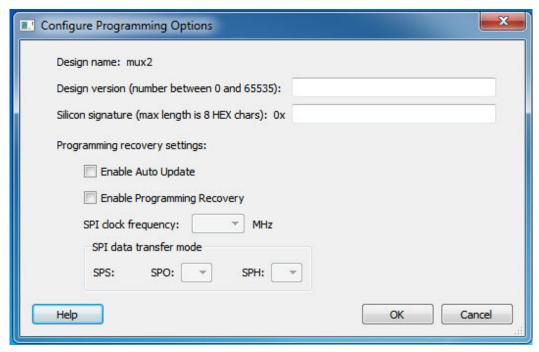

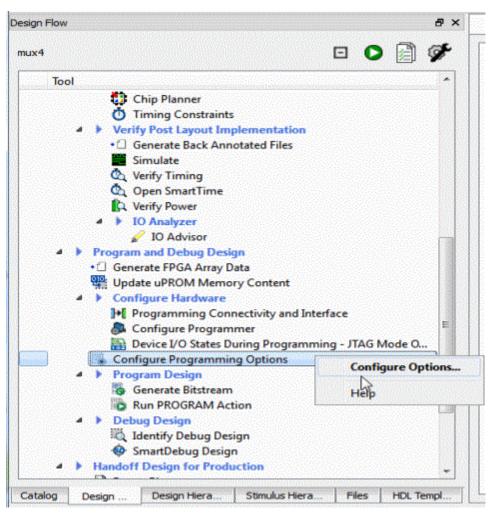

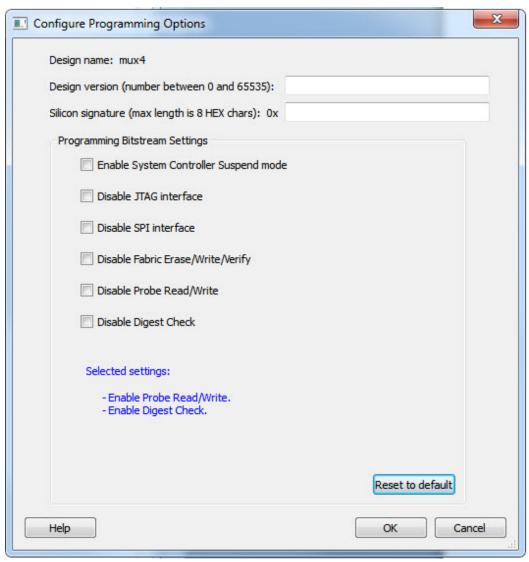

| Configure Programming Options (SmartFusion2 and IGLOO2)                           | 159         |

| Configure Programming Options (RTG4 Only)                                         | 161         |

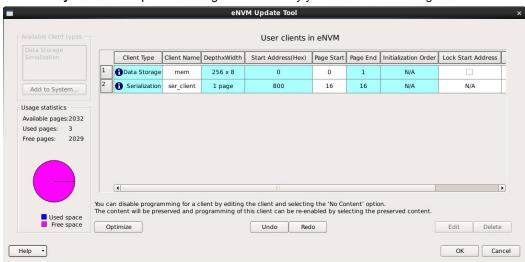

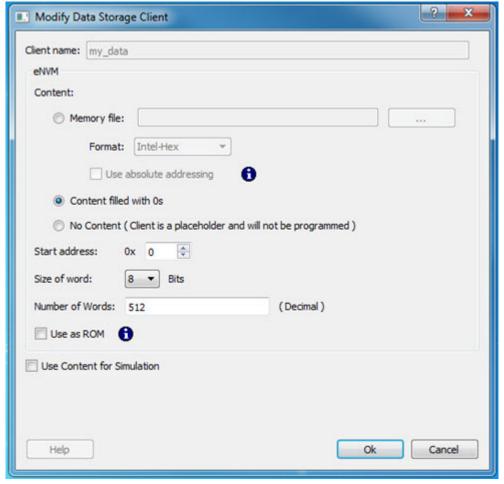

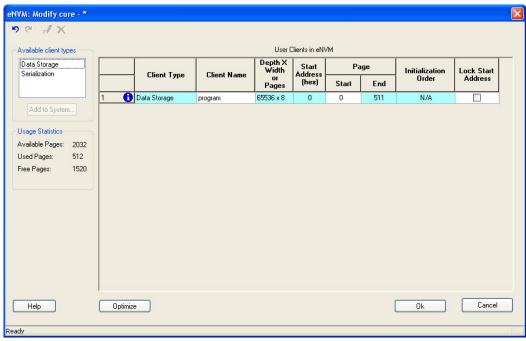

| Update eNVM Memory Content (SmartFusion2 and IGLOO2)                              | 164         |

| Update uPROM Memory Content - RTG4 Only                                           | 167         |

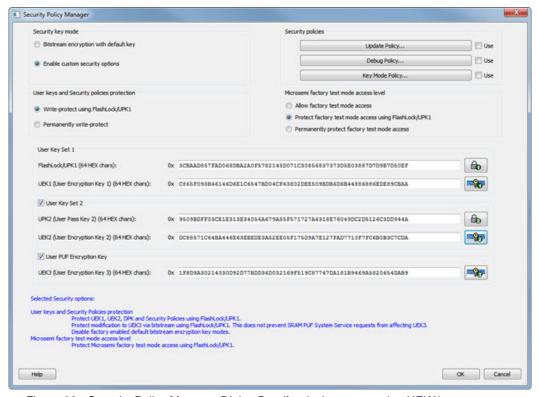

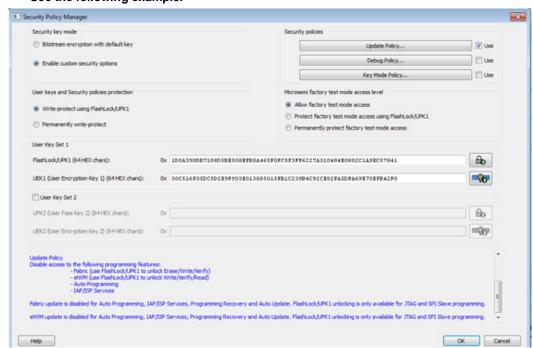

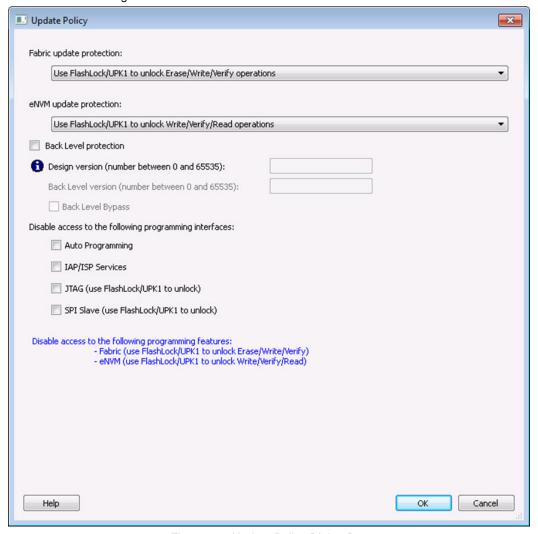

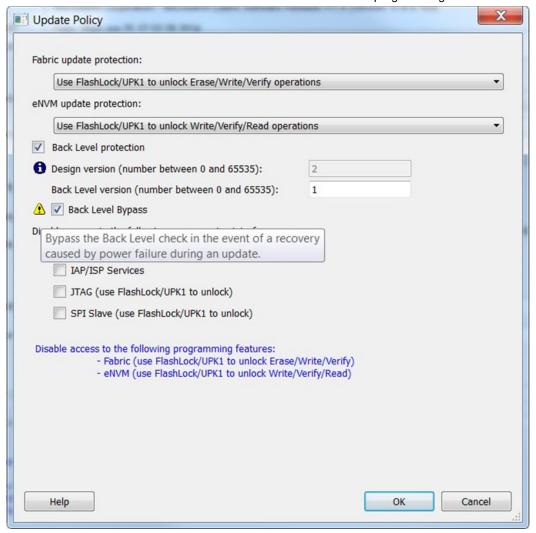

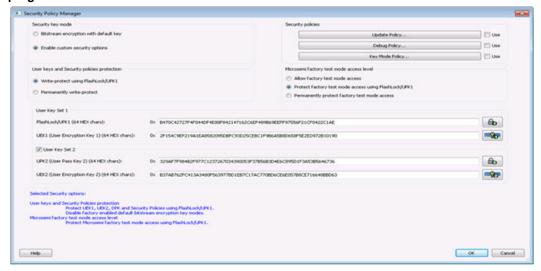

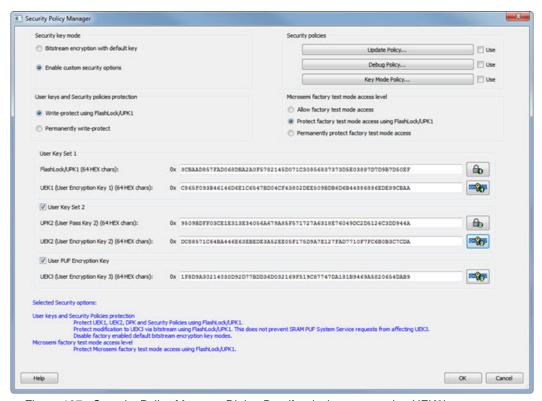

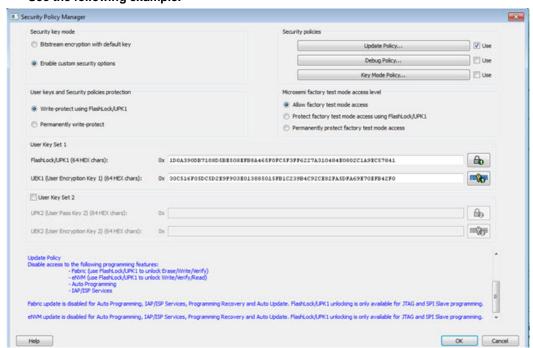

| Configure Security Policy Manager                                                 | 169         |

| Update Policy                                                                     |             |

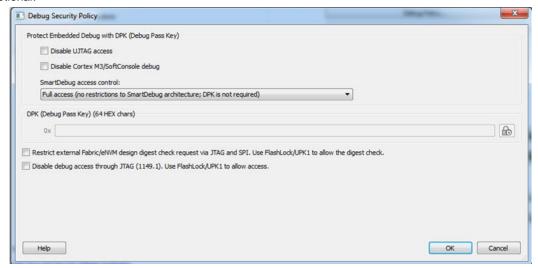

| Debug Security Policy                                                             | 174         |

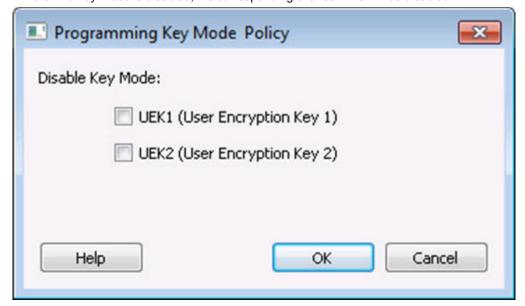

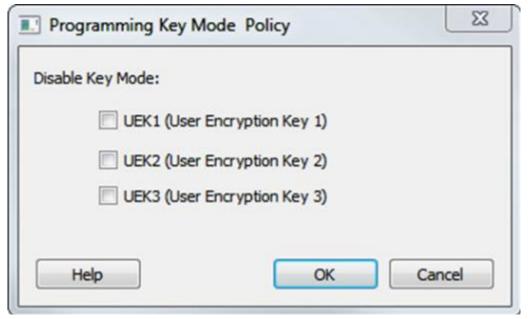

| Key Mode Policy                                                                   | 174         |

| Security Features Frequently Asked Questions                                      | 176         |

| Security Programming Files                                                        | 176         |

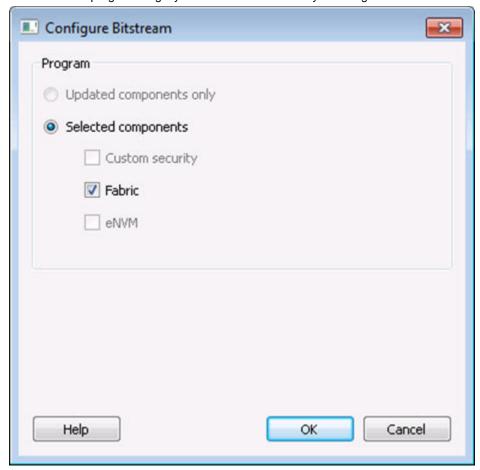

| Configure Bitstream                                                               | 177         |

| Generate Bitstream                                                                | 177         |

| Run PROGRAM Action - SmartFusion2, IGLOO2, and RTG4 Only                          | 178         |

| Program Device - SmartFusion, IGLOO, ProASIC3, and Fusion                         | 178         |

| SmartFusion2 and IGLOO2 Programming - Default Settings                            | 179         |

| SmartFusion2 and IGLOO2 Programming - Custom Settings                             |             |

| Exit Codes (SmartFusion2 and IGLOO2)                                              |             |

| Bitstream Encryption with Default Key in the Security Policy Manager              | 189         |

| Enable Custom Security Options in the Security Policy Manager - SmartFusion2 an   | d IGLOO2190 |

| Programming SmartFusion in the Libero SoC                                         | 193         |

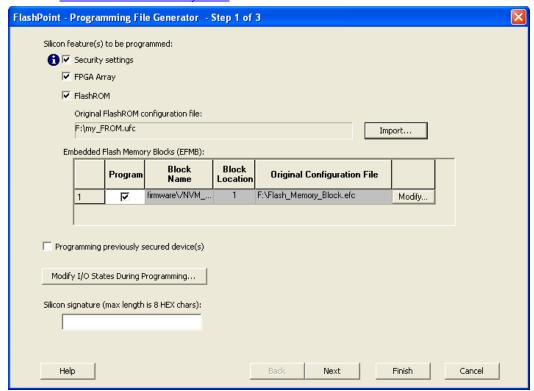

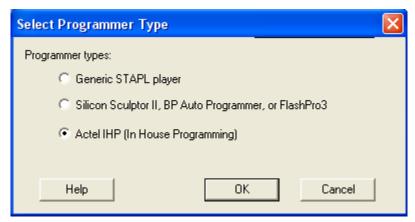

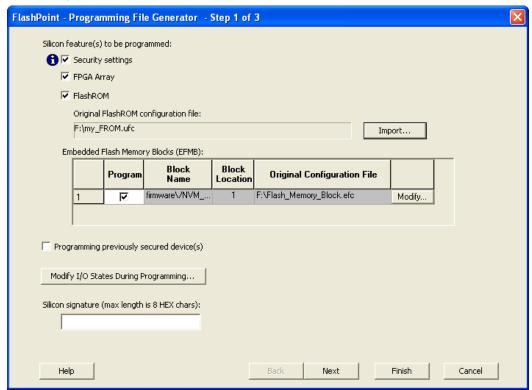

| Generate a Programming File in FlashPoint                                         |             |

| Programming File Types                                                            | 195         |

| Generate a Programming File for SmartFusion                                       | 197         |

| Generate a Programming File for CoreMP7/Cortex-M1 Device Support                  | 197         |

| Generate a Programming File for AFS Device Support - Designer Only                |             |

| Generate a Programming File for Serialization Support in In House Programming (II |             |

| Creating a Programming Database (PDB) File in Designer                            | •           |

| Programming Embedded Flash Memory Block                                           |             |

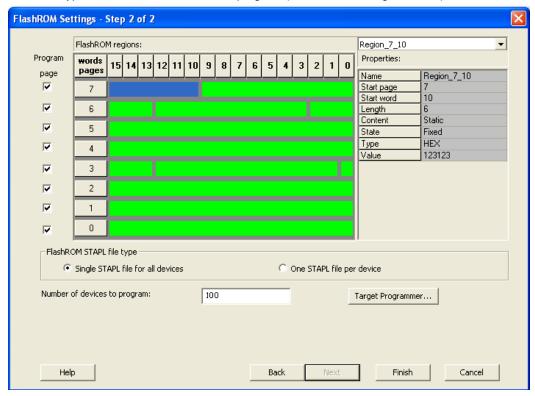

| Programming the FlashROM                                                          |             |

| Silicon Signature                                                                 |             |

| Programming Security Settings                                                     |             |

| Custom Security Levels                                                            |             |

| Reprogramming a Secured Device                                                    |             |

| Custom Serialization Data for FlashROM Region                                     |             |

| Custom Serialization Data File Format                                             |             |

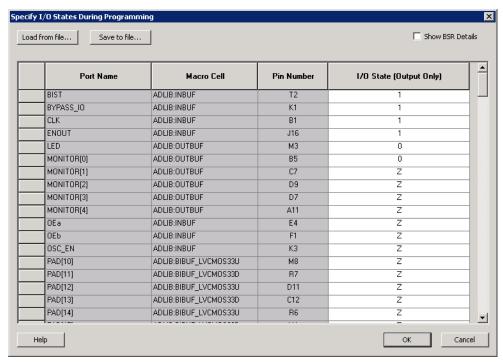

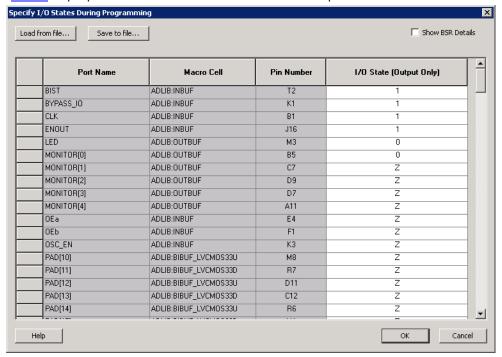

| Specifying I/O States During Programming                                  | 219 |

|---------------------------------------------------------------------------|-----|

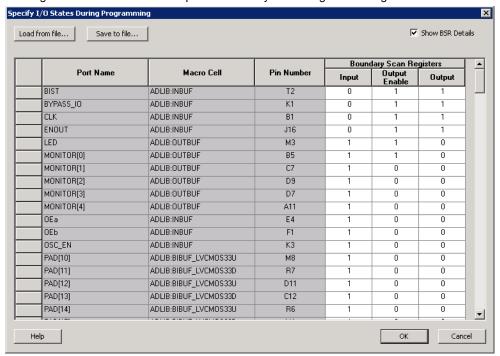

| Custom I/O Settings and Boundary Scan Registers                           | 220 |

| Specifying I/O States During Programming - I/O States and BSR Details     | 220 |

| Specify I/O States During Programming Dialog Box                          | 222 |

| Generate a DAT file                                                       |     |

| FlashLock <sup>®</sup>                                                    |     |

| Generating Bitstream and STAPL files                                      |     |

| ŭ                                                                         |     |

| SmartFusion2 and IGLOO2 Programming Tutorials                             | 226 |

| SPI Programming Tutorial Overview                                         |     |

| Auto Programming                                                          |     |

| In Application Programming (IAP) Tutorial                                 |     |

| Programming Recovery Tutorial                                             |     |

| SmartFusion2 Programming Tutorial Overview                                |     |

| MSS Configuration - eNVM                                                  |     |

| Generate Bitstream                                                        |     |

| Edit Design Hardware Configuration - Device I/O States During Programming |     |

| Configure Security Policy Manager                                         |     |

| Update eNVM Memory Content (SmartFusion2 and IGLOO2)                      |     |

| Program Design - Run PROGRAM Action                                       |     |

|                                                                           |     |

| Handoff Design for Production                                             | 242 |

| Debug Design                                                              | 243 |

| Identify Debug Design                                                     |     |

| SmartDebug                                                                |     |

| omanbobug                                                                 |     |

| Handoff Design for Production                                             | 245 |

| Export Bitstream – SmartFusion2 and IGLOO2                                |     |

| Export Bitstream - RTG4                                                   |     |

| Export Pin Report                                                         |     |

| Export BSDL File                                                          |     |

| Export IBIS Model                                                         |     |

| Export Firmware – SmartFusion2                                            |     |

| Export i illimato Cittata dolone                                          |     |

| Reference Topics, Menus and Dialog Boxes                                  | 251 |

|                                                                           |     |

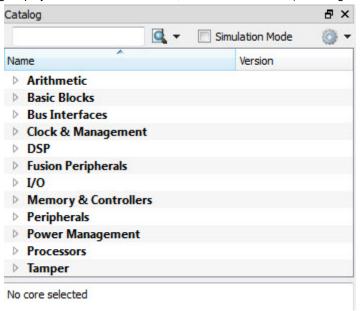

| Catalog                                                                   | 251 |

| Catalog Options Dialog Box                                                | 252 |

| Changing Device Information                                               | 253 |

| Core Manager                                                              | 254 |

| Deleting Files                                                            | 254 |

| Design Hierarchy in the Design Explorer                                   | 255 |

| Design Menu - Libero SoC                                                  |     |

| Designer in Libero SoC                                                    |     |

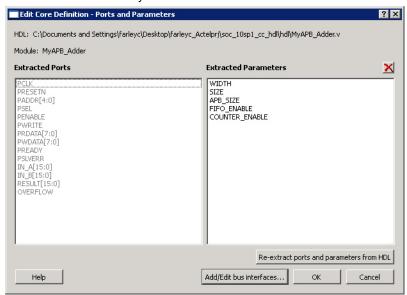

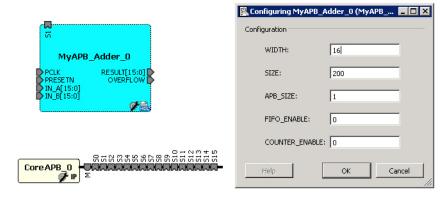

| Edit Core Definition - Ports and Parameters Dialog Box                    |     |

| Edit Menu - Libero SoC                                                    |     |

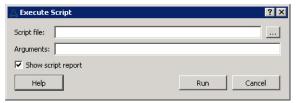

| Execute Script Dialog Box                                          | 258 |

|--------------------------------------------------------------------|-----|

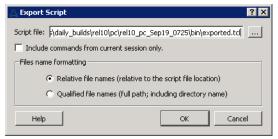

| Export Script Dialog Box                                           |     |

| File Menu - Libero SoC                                             |     |

| Files Tab and File Types                                           | 260 |

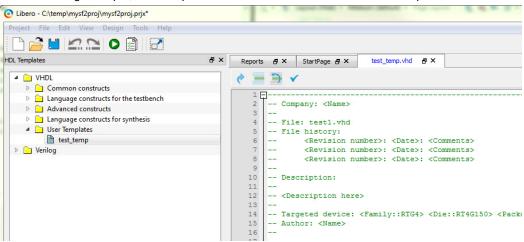

| HDL Templates in Libero SoC                                        |     |

| Help Menu - Libero SoC                                             |     |

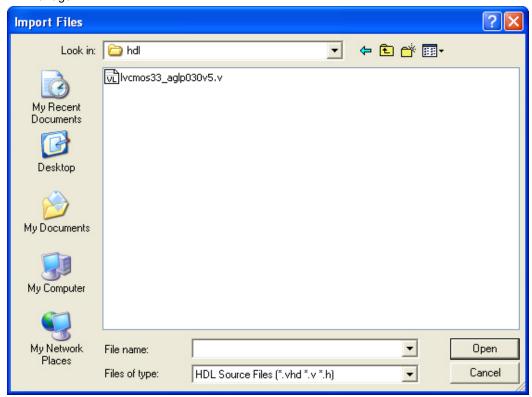

| Import Files Dialog Box (Project Manager)                          |     |

| License Details                                                    |     |

| Link Files                                                         | 264 |

| Log Window                                                         |     |

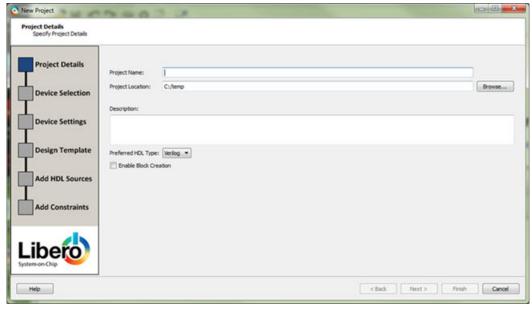

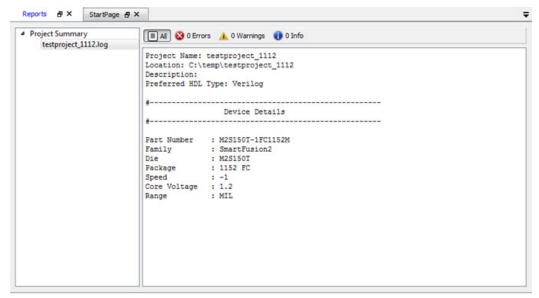

| New Project Creation Wizard – Project Details                      | 265 |

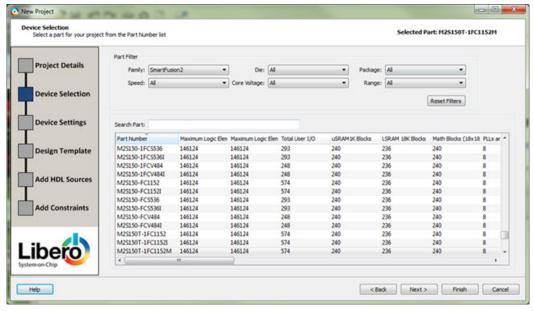

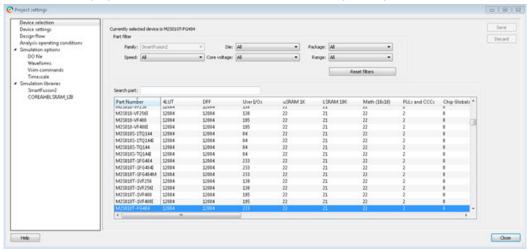

| New Project Creation Wizard – Device Selection                     |     |

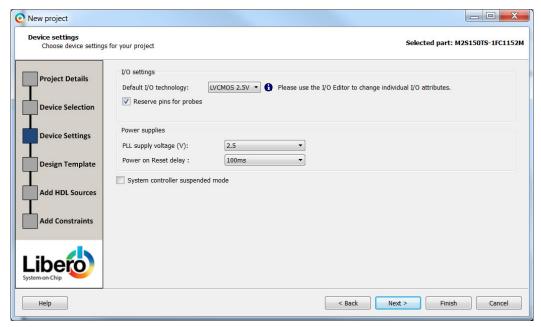

| New Project Creation Wizard – Device Settings                      |     |

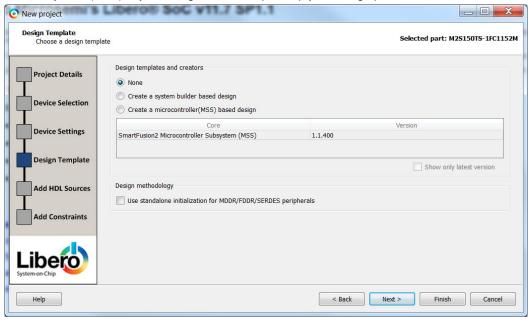

| New Project Creation Wizard – Design Template                      |     |

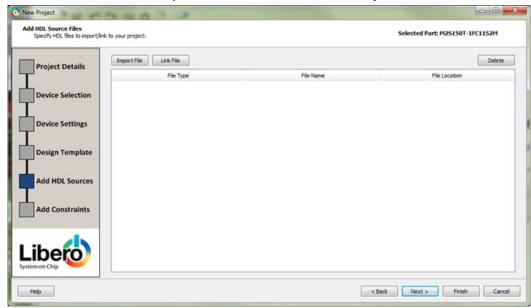

| New Project Creation Wizard – Add HDL Source Files                 |     |

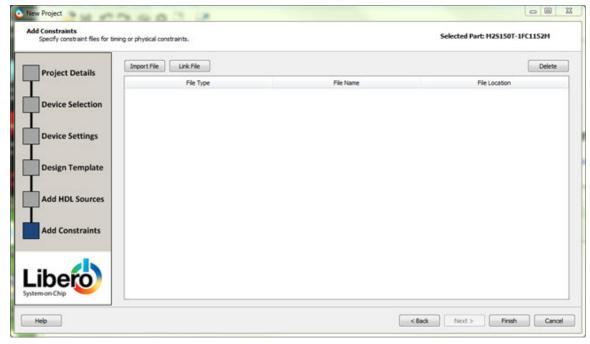

| New Project Creation Wizard - Add Constraints                      |     |

| New File Dialog Box                                                |     |

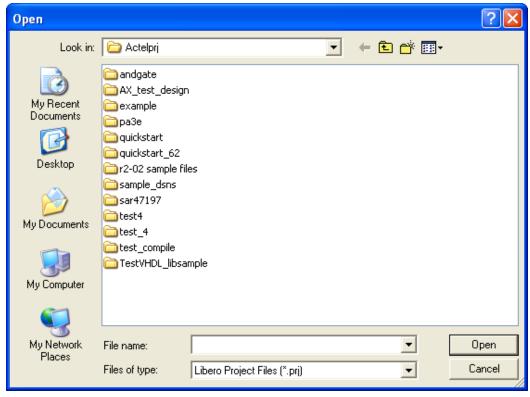

| Open Project Dialog Box                                            |     |

| Opening your Libero SoC project                                    |     |

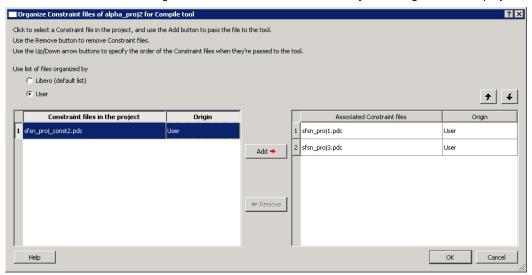

| Organize Constraint Files                                          |     |

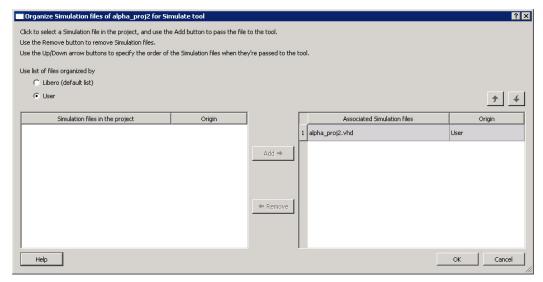

| Organize Simulation Files Dialog Box                               |     |

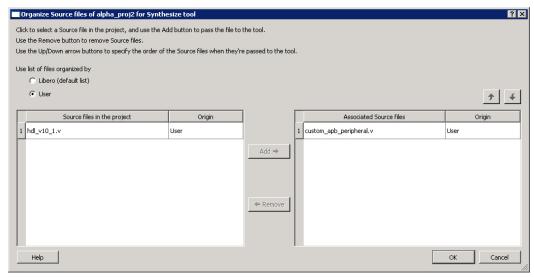

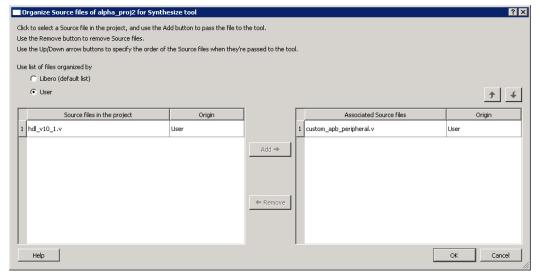

| Organize Source Files Dialog Box – Synthesis                       |     |

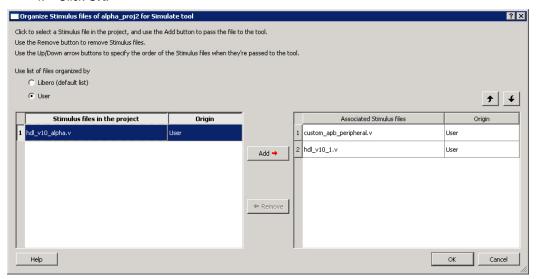

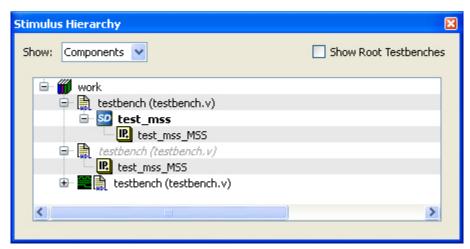

| Organize Stimulus Files Dialog Box                                 |     |

| Physical Synthesis and the Libero SoC                              |     |

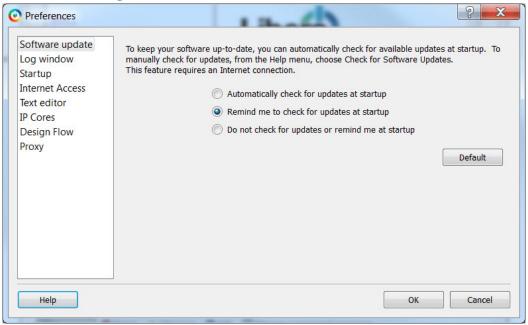

| Preferences                                                        |     |

| User Preferences Dialog Box                                        | 278 |

| Project Menu - Libero SoC                                          |     |

| Project Settings Dialog Box                                        |     |

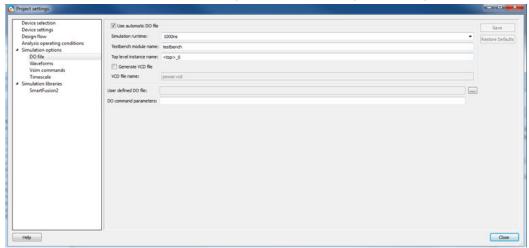

| Project Settings: Simulation                                       |     |

| Project Sources                                                    |     |

| Reserved Microsemi Keywords                                        |     |

| Right-Click (Shortcut) Menu Options in Libero SoC Design Hierarchy |     |

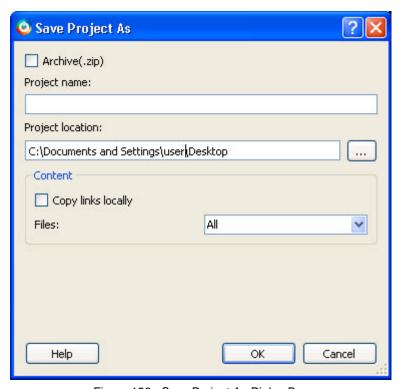

| Save Project As Dialog Box                                         |     |

| Saving Files                                                       | 287 |

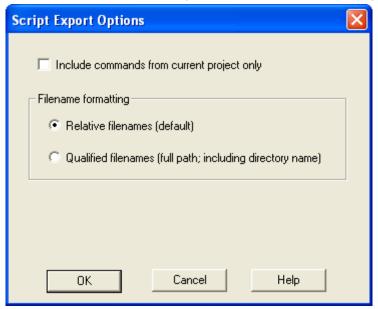

| Script Export Options Dialog Box                                   | 288 |

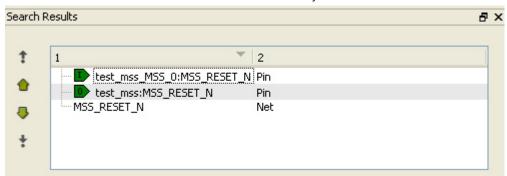

| Search in Libero SoC                                               |     |

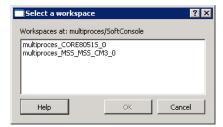

| Select a Workspace Dialog Box                                      |     |

| Organize Source Files Dialog Box – Synthesis                       | 291 |

| Stimulus Hierarchy                                                 |     |

| Text Editor                                                        |     |

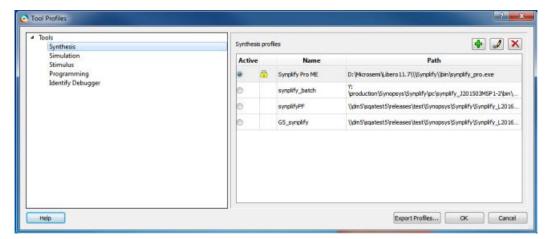

| Tool Profiles Dialog Box                                           |     |

| Tools Menu - Libero SoC                                            |     |

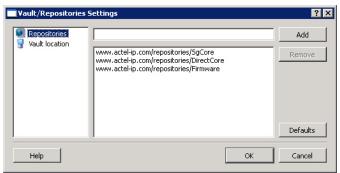

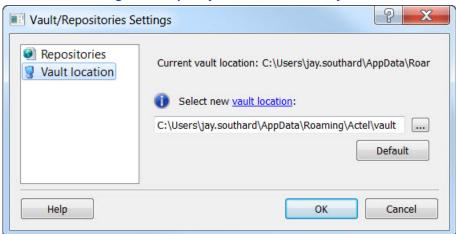

| Vault/Repositories Settings Dialog Box                             |     |

| Videos - Libero SoC                                                |     |

| View Design Datasheet/Report                                       |     |

| View Menu - Libero SoC                                             |     |

#### Classic Constraint Flow User Guide

| Product Support                       | 299 |

|---------------------------------------|-----|

| Tutorials and Training Modules        | 298 |

| Application Notes                     | 297 |

| VHDL Library - Add, Remove, or Rename | 297 |

# Libero SoC Introduction

# Welcome to Microsemi's Libero® SoC

Microsemi Libero® System-on-Chip (SoC) design suite offers high productivity with its comprehensive, easy to learn, easy to adopt development tools for designing with Microsemi's power efficient flash <a href="FPGAs">FPGAs</a>, SoC <a href="FPGAs">FPGAs</a>, and <a href="Rad-Tolerant FPGAs">Rad-Tolerant FPGAs</a>. The suite integrates industry standard Synopsys <a href="Synplify Pro®">Synplify Pro®</a> synthesis and Mentor Graphics <a href="ModelSim®">ModelSim®</a> simulation with best-in-class constraints management, debug capabilities, and secure production programming support.

#### **More Information**

To access datasheets and silicon user guides, visit <a href="www.microsemi.com">www.microsemi.com</a>, select the relevant product family and click the **Documentation** tab. Tutorials, Application Notes, <a href="Development Kits & Boards">Development Kits & Boards</a> are listed in the **Design Resources** tab.

Click the following links for additional information:

- Libero <u>Learn more about Libero SoC</u> including Release Notes, a complete list of devices/packages, and timing and power versions supported in this release.

- Programming <u>Learn more about Programming Solutions</u>

- Power Calculators Find XLS-based estimators for device families

- Licensing <u>Learn more about Libero licensing</u>

# Libero SoC Design Flow (Classic Constraint Flow)

The Libero SoC Build button one click (using default settings).

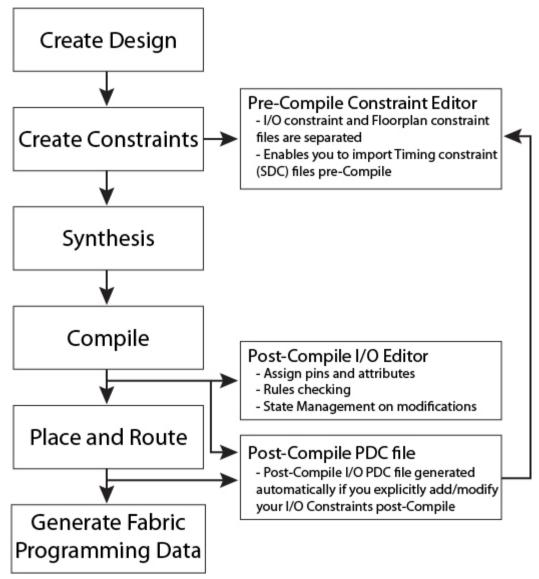

The basic design flow is shown in the figure below.

Figure 1 · Libero SoC Classic Constraint Design Flow

#### **Create Design**

Once you create your design (using <u>System Builder</u>; using the MSS builder - the flow for which is similar to the <u>MSS flow for SmartFusion</u>; <u>create SmartDesign</u>; <u>Create HDL</u>; <u>SmartDesign Testbench</u>) and click the **Build** button the software automatically executes the operations below with default settings (if it encounters no errors).

#### Create Constraints - Pre-Compile

I/O constraint PDC files are separate from Floorplan constraint PDC files; if you have a PDC file that contains both I/O and Floorplan constraints then Libero SoC errors out with an invalid constraint error.

• <u>I/O Constraints</u> - To add an I/O constraint, in the Design Flow window expand Create Constraints, right-click **I/O Constraints** and choose **Import Files**.

- <u>Timing Constraints</u> Enables you to import SDC files pre-Compile.

- <u>Floorplan Constraints</u> Created with the Floorplanner or a text editor; to add a Floorplan constraint, in the <u>Design Flow</u> window expand <u>Create Constraints</u>, right-click <u>Floorplan Constraints</u> and choose <u>Import Files</u>.

#### **Synthesis**

Double-click **Synthesize** to run <u>synthesis</u> on your design automatically; automatic synthesis uses the default settings in your synthesis tool.

#### **Compile**

To <u>compile</u> your design with custom settings, right-click **Compile** in the Design Flow window and choose **Configure Options**.

#### **Place and Route**

<u>Place and Route</u> runs automatically with default settings as part of the push-button design flow in Libero SoC.

#### Edit Constraints - Post-Compile

<u>I/O Constraints</u> - The Post-Compile I/O Editor displays all assigned and unassigned I/O macros and their attributes in a spreadsheet format; use this editor to view, sort, select, edit, lock and unlock assigned attributes.

The post compile editor ensures that the Compile/Place and Route state is maintained (you do not have to rerun Compile or Place and Route), if you make changes to the attributes that do not require it.

However, if you modify the I/O PDC file directly, it is equivalent to modifying the source file of the design, which means the tools starting from Compile will become out of date because one of the source files was modified.

- <u>Timing Constraints</u> Run SmartTime to perform Min/Max analysis and manage timing constraints.

- Floorplan Constraints Use to create and edit regions on your chip and assign logic to these regions.

#### **Generate Fabric Programming Data**

Generates programming data for your design.

#### IGLOO, ProASIC3, and Fusion Programming

SmartFusion, IGLOO, ProASIC3, and Fusion devices use the FlashPoint program file generator to create a programming file. For SmartFusion, IGLOO, and ProASIC3, the FlashPoint interface also enables the advanced security features.

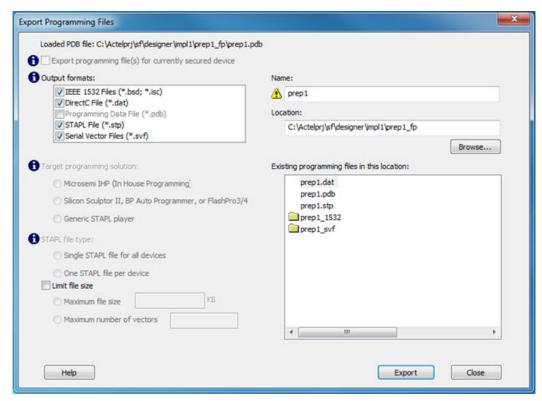

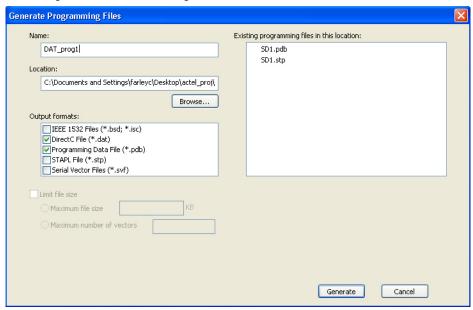

To open FlashPoint, expand Implement Design, right-click Generate Programming Data, and choose **Open Interactively**. FlashPoint allows you to generate the following programming files:

- IEEE 1532 files (\*.bsd, \*.isc)

- DirectC files (\*.dat)

- Programming Data File (\*.pdb)

- STAPL file (\*.stp)

- Serial Vector Files (\*.svf)

You must have completed your design to generate your programming (\*.stp or STAPL) file.

#### SmartFusion2, IGLOO2, and RTG4 Programming

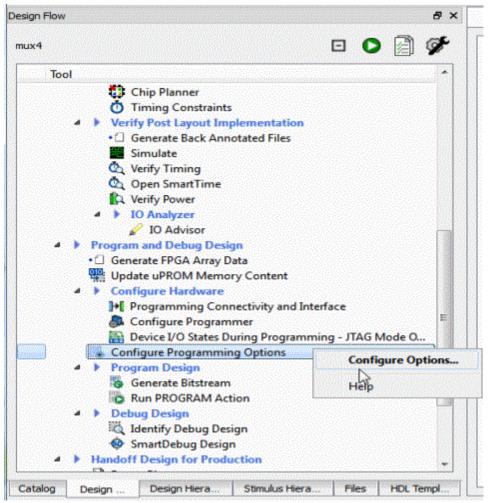

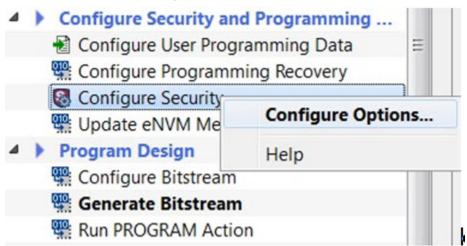

You do not have to open FlashPro or FlashPoint to program your SmartFusion2 device. All programming functionality is available from within the Design Flow window, including:

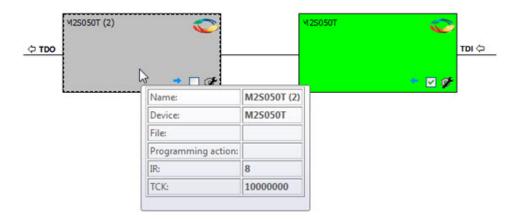

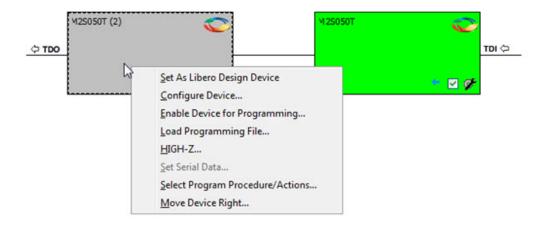

Programming Connectivity and Interface - Organizes your programmer(s) and devices.

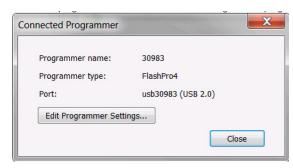

<u>Programmer Settings</u> - Opens your programmer settings; use if you wish to program using settings other than default.

<u>Device I/O States During Programming</u> - Sets your device I/O states during programming; use if your design requires that you change the default I/O states.

<u>Security Policy Manager</u> - Enables you to set your Secured Programming Use Model, User Key Entry and Security Policies for your design.

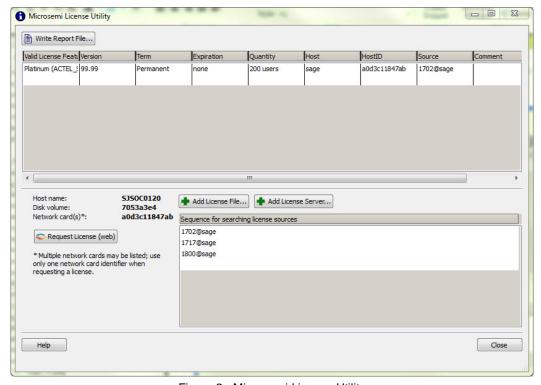

### Microsemi License Utility

The <u>Microsemi SoC Products Group LicenseTroubleshooting Guide</u> answers the most common licensing-related frequently asked questions.

The Microsemi License Utility enables you to check and update your license settings for the Libero SoC software. It displays your current license settings, the license host-id for the current host, and allows you to add a new license file to your settings.

To start the Microsemi License Utility, run it from **Start > All Programs > Microsemi Libero SoC v**x.xx> **Microsemi License Utility**.

To request a license, click **Request License** to go to the Microsemi license website. You can select and copy (right-click, **Copy**) the disk volume value displayed in the window and paste the value into the Microsemi license web form.

The following licenses are available:

- 1-year Platinum Purchased license that supports all devices

- 1-year Gold Purchased licenses that supports a smaller set of devices than Platinum

- 1-year Silver Free license that supports a smaller set of devices than Gold

- 30-day Evaluation Free license that supports all devices but programming is disabled

When you have received your license file, follow the instructions and save the license to your local disk. In the Microsemi License Utility window, click **Add License File** and browse/select the license file from your disk. If you are using a floating license, click **Add License Server** and enter the Port Number and Name of the license server host.

The list of features for which you are licensed will show all versions, but your license must have a version equal to or greater than your design tools release version in order for the libero.exe and designer.exe tools to run.

The list at the lower right shows the order in which the license files are read, with the first file read at the top of the list.

Click Write Report File to view and/or print the Microsemi Tools Licenses Report, or to save it as a TXT file.

Figure 2 · Microsemi License Utility

# File Types in Libero SoC

When you create a new project in Libero SoC it automatically creates new directories and project files. Your project directory contains all of your local project files. When you <u>import</u> files from outside your current project, the files are copied into your local project folder.

The Project Manager enables you to manage your files as you import them. If you want to store and maintain your design source files and design constraint files in a central location outside the Project location, Libero gives you the option to link them to your Libero project folders when you first create your project. These linked files are not copied but rather linked to your project folder.

Depending on your project preferences and the version of Libero SoC you installed, the software creates directories for your project.

The top level directory (<project\_name>) contains your \*.prjx file; only one \*.prjx file is enabled for each Libero SoC project. If you associate Libero SoC as the default program with the \*.prjx file (Project > Preferences > Startup > Check the default file association (.prjx) at startup), you can double-click the \*.prjx file to open the project with Libero SoC.

**component** directory - Stores your SmartDesign components (SDB and CXF files) and the \*\_manifest.txt file for each design components in your Libero SoC project. Refer to the \*\_manifest.txt file if you want to run synthesis, simulation, and firmware development with your own point tools outside the Libero SoC environment. For each design component, Libero SoC generates a <component\_name>\_manifest.txt file which stores the file name and location of:

- · HDL source files to be used for synthesis and simulations

- · Stimulus files and configuration files for simulation

- Firmware files for software IDE tools

- Configuration files for programming

· Configuration files for power analysis.

Refer to the SmartFusion2/IGLOO2 Custom Flow User Guide for details about how to run synthesis, simulation, firmware development, programming, and power analysis outside the Libero SoC environment. **constraint** directory - All your constraint files (SDC timing constraint files, floorplanning PDC files, I/O PDC files, Netlist Attributes NDC files)

**designer** directory - ADB files (Microsemi Designer project files), \*\_ba.sdf, \*\_ba.v(hd), STP, PRB (for Silicon Explorer), TCL (used to run designer), impl.prj\_des (local project file relative to revision), designer.log (logfile)

Note: The Microsemi ADB file memory requirement is equivalent to 2x the size of the ADB file. If your computer does not have 2x the size of your ADB file's memory available, please make memory available on your hard drive.

hdl directory - all hdl sources. \*.vhd if VHDL, \*.v and \*.h if Verilog

simulation directory - meminit.dat, modelsim.ini files, \*.bfm files and \*.vec file, run.do file for simulation.

smartgen directory - GEN files and LOG files from generated cores

stimulus directory - BTIM, Verilog, and VHDL stimulus files

**synthesis** directory - \*.edn, \*\_syn.prj (Synplify log file), \*.psp (Precision project file), \*.srr (Synplify logfile), precision.log (Precision logfile), \*.tcl (used to run synthesis) and many other files generated by the tools (not managed by Libero SoC)

viewdraw directory - viewdraw.ini files

#### **Internal Files**

Libero SoC generates the following internal files. They may or may not be encrypted. They are for Libero SoC housekeeping and are not for users.

| File                      | File Extension | Remarks                 |

|---------------------------|----------------|-------------------------|

| Routing Segmentation File | *.seg          |                         |

| Combiner Info             | *.cob          |                         |

| Hierarchical Netlist      | *.adl          |                         |

| Flattened Netlist         | *.afl          |                         |

| Location file             | *.loc          |                         |

| map file                  | *.map          | Fabric Programming File |

| tieoffs.txt               | *.txt          | RTG4 devices only       |

## Software Tools - Libero SoC

The Libero SoC integrates design tools, streamlines your design flow, manages design and log files, and passes design data between tools.

For more information on Libero SoC tools, visit:

http://www.microsemi.com/products/fpga-soc/design-resources/design-software/libero-soc#overview

| Function                                                                                            | Tool                            | Company            |

|-----------------------------------------------------------------------------------------------------|---------------------------------|--------------------|

| Project Manager, HDL Editor, Core Generation                                                        | Libero SoC                      | Microsemi<br>SoC   |

| Synthesis                                                                                           | Synplify <sup>®</sup><br>Pro ME | Synopsys           |

| Simulation                                                                                          | ModelSim <sup>®</sup><br>ME     | Mentor<br>Graphics |

| Timing/Constraints, Power Analysis, Netlist Viewer, Floorplanning, Package Editing, Place-and-Route | Libero SoC                      | Microsemi<br>SoC   |

**Project Manager, HDL Editor** targets the creation of HDL code. HDL Editor supports VHDL and Verilog with color, highlighting keywords for both HDL languages.

**Synplify Pro ME** from Synopsys is integrated as part of the design package, enabling designers to target HDL code to specific devices.

Microsemi SoC software package includes:

- ChipPlanner displays I/O and logic macros in your design for floorplanning

- Netlist Viewer design schematic viewer

- · SmartPower power analysis tool

- SmartTime static timing analysis and constraints editor

ModelSim ME from Mentor Graphics enables source level verification so designers can verify HDL code line by line. Designers can perform simulation at all levels: behavioral (or pre-synthesis), structural (or post-synthesis), and back-annotated (post-layout), dynamic simulation. (ModelSim is supported in Libero Gold and Platinum only.)

# Frequently Asked Questions - Libero SoC

The collection of Frequently Asked Questions is useful for anyone that is new to Libero SoC. All the information listed below is explained in detail in other sections of the help, but the information is summarized here for easy reference. Click any question to go to the corresponding explanation.

#### **Libero SoC Frequently Asked Questions**

- 1. How do I set my Multi-Pass place and route options?

- 2. How do I set FlashPro security options?

- 3. How do I instantiate my HDL in SmartDesign?

- 4. How do I add a bus interface to my HDL code and then add it to SmartDesign?

- I don't see any DirectCore IP's in the Catalog but I have both Libero IDE 9.1 and Libero SoC 10.0 installed. Where are the DirectCore IP's?

- 6. How do I assign I/O/s in Libero SoC?

- 7. How do I make sure that my design is using the latest driver(s)?

- 8. How do I improve the timing of my design?

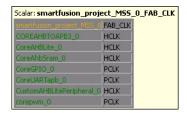

- 9. How do I manage clocks?

- 10. How do I write a testbench?

#### **Firmware Cores Frequently Asked Questions**

- 1. Where are the firmware files generated?

- 2. Why are some firmware in italics?

- 3. Why am I getting the following error on generation? "Error: 'Missing Core Definition': Core 'Actel:Firmware:MSS\_SPI\_Driver:2.0.101' is missing from the vault."?

- 4. Why is my firmware view empty?

- 5. Why are there multiple firmware instances of the same type?

#### **Libero SoC Frequently Asked Questions**

#### How do I set my Multi-Pass place and route options?

The steps to run Multi-Pass place and route vary depending on the device family.

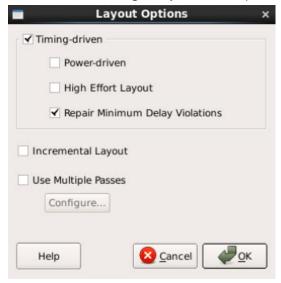

For SmartFusion, IGLOO, ProAsic and Fusion: In the Design Flow window, expand Implement Design, right-click Place and Route and choose Open Interactively. Designer opens. Click Layout to open the Layout Options dialog box and choose Use Multiple Pass. Click the Configure button to open the Multi-Pass Configurator. Set your Multi-Pass Options. Once Layout is complete, save your ADB to retain your custom place and route options.

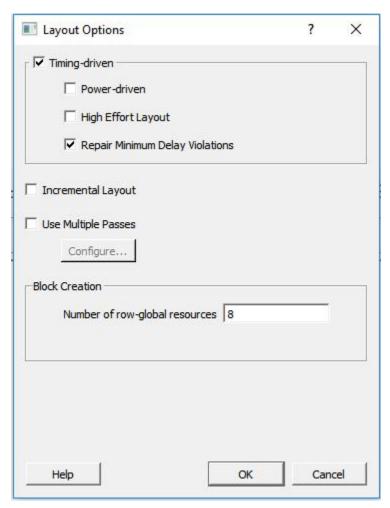

For SmartFusion2, IGLOO2, RTG4: In the Design Flow window, expand Implement Design, right-click Place and Route and choose Configure Options. When the Layout Options dialog box appears, check the Use Multiple Passes option and click Configure. When the Multi-Pass configuration dialog box appears, set your Multi-Pass options.

#### How do I set FlashPro security options?

In the Libero SoC Design Flow window, expand **Program Design**, right-click **Program Device** and choose **Open Interactively**. FlashPro opens and enables you to set/change your security options. See the FlashPro help for more information.

#### How do I instantiate my HDL in SmartDesign?

Import your HDL file into the Libero SoC (File > Import Files). After you do this, your HDL module appears in the Project Manager <u>Hierarchy</u>. Then, drag-and-drop it from the Hierarchy onto your SmartDesign Canvas.

#### How do I add a bus interface to my HDL code and then add it to SmartDesign?

If you want to add a bus interface to your HDL code and then add it to SmartDesign, see the Adding or Modifying Bus Interfaces in SmartDesign topic.

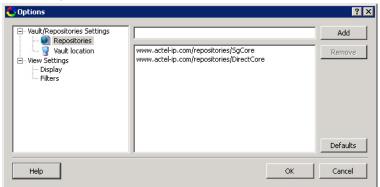

# I don't see any DirectCore IP's in the Catalog but I have both Libero IDE 9.1 and Libero SoC 10.0 installed. Where are the DirectCore IP's?

Make sure the vault location is correct. Click the <u>Catalog</u> Options button to open the <u>Catalog Options</u> dialog box. Then check and, if necessary, update your vault location.

#### How do I assign I/O's in Libero SoC?

In the Design Flow window, expand **Implement Design**, then expand **Constrain Place and Route**. Right-click **Edit I/O Attributes** and choose **Open Interactively** to open the <u>I/O Attribute Editor</u>.

#### How do I make sure that my design is using the latest driver(s)?

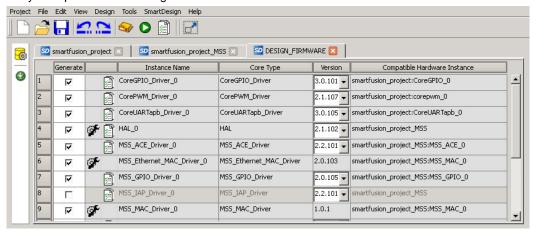

In the Design Flow tab, expand **Create Design** and double-click **View/Configure Firmware Cores** to view the <u>DESIGN\_FIRMWARE tab</u>. The Firmware table lists the compatible firmware and drivers based on the hardware peripherals that you have used in your design. Use the Version drop down menus to check for the latest firmware and firmware drivers.

#### How do I improve the timing of my design?

The SmartTime tool enables you to <u>set clock constraints</u>, <u>analyze timing</u>, identify critical paths, and find the minimum cycle time that does not result in a timing violation.

To improve the timing of your design:

- 1. Run timing analysis to identify timing violations.

- 2. View the paths with timing violations.

- 3. Modify timing constraints on the critical path(s) in order to meet your timing requirements.

- 4. Run Timing-Driven Place and Route.

For more information on improving timing, see the <u>Analysis and Optimization application notes</u>. The <u>Designing for Performance on Flash-Based FPGAs application note</u> is a good starting point.

#### How do I manage clocks?

<u>Specify clock constraints</u> in your design. See the sections on <u>explicit clocks</u>, <u>potential clocks</u> and <u>clock</u> networks for more information on clocks in Libero SoC.

#### How do I write a testbench?

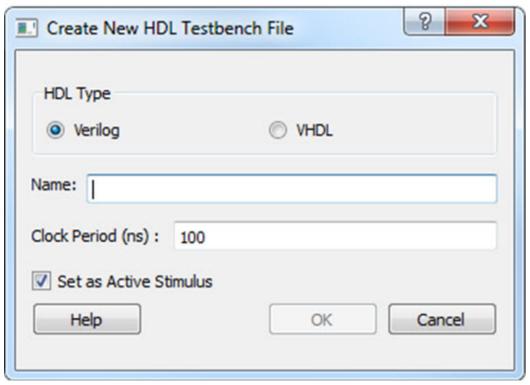

You can write or edit a testbench manually using the <u>HDL editor</u>, or you can create a new HDL testbench and automatically populate it with all your design information with <u>Create New HDL Testbench</u> in Libero SoC. Create New HDL Testbench is in the Design Flow window under **Create Design**.

Testbench file are generated automatically when you generate a SmartDesign. You can find them in your Files window in Libero SoC (View > Window > Files).

# Firmware Cores Frequently Asked Questions

#### Where are the firmware files generated?

The firmware files are generated to the firmware working directory ct>\firmware. Your software IDE workspace is generated to ct>\<software</pre> IDE tool chain>.

#### Why are some firmware in italics?

This indicates the firmware is in the IP repository but not in your local IP vault. You must download it to your local IP vault so that the Libero SoC will generate the firmware files.

Why am I getting the following error on generation? "Error: 'Missing Core Definition': Core 'Actel:Firmware:MSS\_SPI\_Driver:2.0.101' is missing from the vault."?

This happens when a firmware that is in your design but the VLNV definition could not be found in your IP vault. This can happen if you:

- Changed your vault settings to point to another vault

- Opened a project that was created on another machine

#### Why is my firmware view empty?

Check that you are pointing to the proper firmware repository:

www.actel-ip.com/repositories/Firmware

Check with your network administrator to make sure you can communicate with Microsemi's IP repository URL.

#### Why are there multiple firmware instances of the same type?

Some firmware cores have configurable options, and in certain cases you will have two peripherals of the same firmware VLNV. In this situation, you may want to configure each peripheral driver separately.

# Software IDE Integration

Libero SoC simplifies the task of transitioning between designing your FPGA to developing your embedded firmware.

Libero SoC manages the firmware for your FPGA hardware design, including:

- Firmware hardware abstraction layers required for your processor

- Firmware drivers for the processor peripherals that you use in your FPGA design.

- Sample application projects are available for drivers that illustrate the proper usage of the APIs

You can see which firmware drivers Libero SoC has found to be compatible with your design by opening the <u>Firmware View</u>. From this view, you can change the configuration of your firmware, change to a different version, read driver documentation, and generate any sample projects for each driver.

Libero SoC manages the integration of your firmware with your preferred Software Development Environment, including SoftConsole, Keil, and IAR Embedded Workbench. The projects and workspaces for your selected development environment are automatically generated with the proper settings and flags so that you can immediately begin writing your application.

#### See Also

Exporting Firmware and the Software IDE Workspace

Libero SoC Frequently Asked Questions

Running Libero SoC from your Software Tool Chain

View/Configure Firmware Cores

# Running Libero SoC from your Software Tool Chain

When launched from your software toolchain, Libero SoC becomes solely an MSS configurator. This can be useful if you are responsible for the embedded code development for the SmartFusion device and are more comfortable in your existing software tool chain.

Any FPGA fabric development needs to be done using the regular Libero® SoC tool flow. Using the Libero SoC in the software toolchain mode only enables you to configure the SmartFusion Microcontroller Subsystem (MSS) and not the FPGA fabric.

The MSS Configurator can be integrated in any software development IDE that supports external tools. Configure your IDE to start the Libero SoC executable and use the parameters below to customize your interface. For SoftConsole, Keil and IAR the parameters are:

"PROJECT\_LOCATION: <path>" //Project directory location, and the location of your generated MSS files.

"DESIGN\_NAME: < name > " //Name of your design.

"STARTED\_BY:<tool>" //Identifies which tool invoked the MSS Configurator; can be SoftConsole, Keil, or IAR EWARM

#### See Also

Exporting Firmware and the Software IDE Workspace

Libero SoC Frequently Asked Questions

Software IDE Integration

View/Configure Firmware Cores

# Create Design

### System Builder

System Builder is a graphical design wizard that enables you to enter high-level design specifications for SmartFusion2 or IGLOO2.

System Builder takes you through the following steps:

- · Asks basic questions about your system architecture and peripherals

- Builds a correct-by-design complete system

System Builder automatically configures the silicon features you select. To complete the design, add your custom logic or IP and connect them to your System Builder-generated design.

See the <u>SmartFusion2 System Builder documentation</u> or the <u>IGLOO2 System Builder documentation</u> for a complete family-specific explanation of the tool.

## Instantiate a SmartFusion MSS in your Design

You can configure peripherals within the SmartFusion MSS, such as the ARM® Cortex<sup>TM</sup>-M3, embedded nonvolatile memory (eNVM), Ethernet MAC, timer, UART, and SPI to suit your needs. The MSS operates standalone without any dependencies on other logic within the device; however, designs that require functionality beyond a standalone MSS are handled by using SmartDesign to add user logic in the SmartFusion FPGA fabric.

You can instantiate a Microcontroller Subsystem into your design from the New Project Creation Wizard when you start a new SmartFusion project, or from the Design Flow window after you have created a new project.

To instantiate a SmartFusion MSS from the New Project Creation Wizard you must enable **Use Design Tool** (under **Design Templates and Creators**) and click to select **SmartFusion Microcontroller Subsystem (MSS)** from the list.

If you opted not to use a Design Tool when you created your project, in the Design Flow window expand **Create Design** and double-click **Configure MSS**. This opens the **Add Microcontroller Subsystem** dialog box. Enter your **Design Name** and click **OK** to continue. A SmartDesign Canvas appears with the MSS added to your project; double-click the MSS to view and <u>configure MSS components</u>.

# Configure the SmartFusion MSS

Documents for specific SmartFusion MSS peripherals are available on the Peripheral Documents web page.

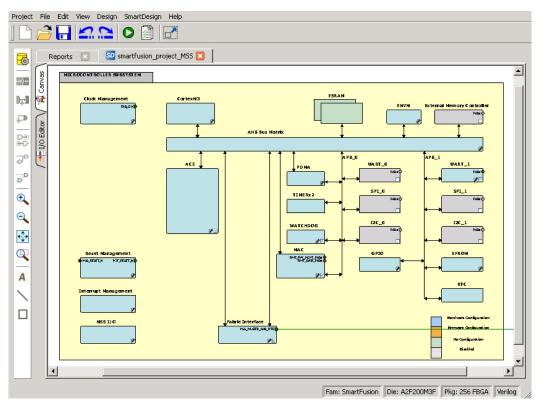

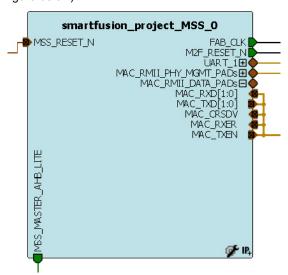

The SmartFusion Microcontroller Subsystem (MSS) Configurator (as shown in the figure below) contains the elements listed below. Double-click any element in the MSS to configure it; click the checkbox (if available) to enable or disable it in your design.

#### MSS ARM® Cortex™-M3

#### **Peripherals**

- ACE Configuration

- ACE Simulation

- AHB Bus Matrix Configuration

- Clock Configuration

#### Classic Constraint Flow User Guide

- · Configurator Overview

- Embedded FlashROM (eFROM) Configuration

- Embedded Nonvolatile Memory (eNVM) Configuration

- Ethernet MAC Configuration

- External Memory Controller (EMC) Configuration

- Firmware

- GPIO Configuration

- I2C Configuration

- Interrupt Management

- I/O Configuration

- I/O Editor

- Peripheral DMA Configuration

- Real Time Counter (RTC) Configuration

- Reset Management Configuration

- SPI Configuration

- Timer Configuration

- UART Configuration

- Watchdog Configuration

#### **Fabric**

• Dedicated Fabric Clock Conditioning Circuit with PLL Integration

#### Interfaces

- How to Create a MSS and Fabric AMBA AHBLite Design (MSS Master Mode)

- How to Create a MSS and Fabric AMBA APB3 Design (MSS Master Mode)

- How to Create a MSS and Fabric AMBA AHBLite/APB3 Design (MSS Master Mode)

#### **SmartFusion SmartDesign Documents**

- SmartDesign MSS Canvas

- SmartDesign MSS Simulation

- SmartDesign MSS Running the MSS Configurator in your Software Tool Chain

Figure 3 · SmartFusion MSS

### Generate SmartFusion MSS Files

See the MSS Configurator help for more information on generating SmartFusion MSS files.

Click the **Generate Component** button to create your SmartFusion MSS files.

The MSS Configurator generates the following files:

- HDL files for the MSS design and its sub-components: MSS CCC, etc. HDL files are automatically managed by the Libero SoC and passed to the Synthesis and Simulation point tools.

- EFC File. MSS hardware configuration that is loaded into eNVM. FlashPro automatically detects this file and includes it in your final programming file.

- UFC file. Contains your Embedded FlashROM configuration and data. FlashPro automatically detects this file and includes it in your final programming file.

- Firmware drivers and memory maps are exported into the project

firmware drivers Libero SoC automatically generates a Software IDE project that includes your Firmware drivers. If you are not using a software project automatically created by Libero, you can import this directory into your Software IDE project.

- Testbench HDL and BFM script for the MSS design: These files are managed by Libero SoC and automatically passed to the Simulation point tool.

- PDC files for the MSS and the top-level design: These files are managed by Libero SoC and automatically integrated during Compile and Layout.

# Instantiate a SmartFusion2 MSS in your Design

You can configure peripherals within the SmartFusion2 MSS, such as the ARM® Cortex™-M3, embedded nonvolatile memory (eNVM), Ethernet MAC, timer, UART, and SPI to suit your needs. The MSS operates standalone without any dependencies on other logic within the device; however, designs that require functionality beyond a standalone MSS are handled by using SmartDesign to add user logic in the SmartFusion2 FPGA fabric.

You can instantiate a Microcontroller Subsystem into your design from the New Project Creation Wizard when you start a new SmartFusion2 project, or from the Design Flow window after you have created a new project.

To instantiate a SmartFusion2 MSS from the New Project Creation Wizard you must enable **Use Design Tool** (under **Design Templates and Creators**) and click to select **SmartFusion2 Microcontroller Subsystem (MSS)** from the list.

If you opted not to use a Design Tool when you created your project, in the Design Flow window expand **Create Design** and double-click **Configure MSS**. This opens the **Add Microcontroller Subsystem** dialog box. Enter your **Design Name** and click **OK** to continue. A SmartDesign Canvas appears with the MSS added to your project; double-click the MSS to view and <u>configure MSS components</u>.

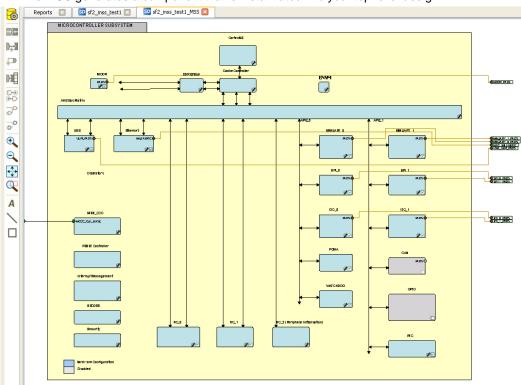

# Configure the SmartFusion2 MSS

Documents for specific SmartFusion2 MSS peripherals are available on the <u>Peripheral Documents web page</u>.

The SmartFusion2 Microcontroller Subsystem (MSS) Configurator (as shown in the figure below) contains the elements listed below. Double-click any element in the MSS to configure it; click the checkbox (if available) to enable or disable it in your design.

#### MSS ARM® Cortex™-M3

#### **Peripherals**

- MSS CAN

- MSS Peripheral DMA (PDMA)

- MSS GPIO

- MSS I2C

- MSS Ethernet MAC

- MSS DDR Controller (MDDR)

- MSS MMUART

- MSS Real Time Counter (RTC)

- MSS Embedded Nonvolatile Memory (eNVM)

- MSS SPI

- MSS USB

- MSS Watchdog Timer

#### **Fabric Interfaces**

• MSS Fabric Interface Controllers (FICs)

#### **Additional Information**

- MSS Cache Controller

- MSS DDR Bridge Controller

- MSS AHB Bus Matrix

- MSS Clocks Configurator (MSS CCC)

- MSS Interrupts Controller

- MSS Reset Controller

- MSS SECDED Configurator

- MSS Security Configurator

The MSS generates a component that is instantiated into your top-level design.

Figure 4 · Microcontroller Subsystem Configurator

## Generate SmartFusion2 MSS Files

See the MSS Configurator help for more information on generating SmartFusion2 MSS files.

Click the **Generate Component** button to create your SmartFusion2 MSS files.

The MSS Configurator generates the following files:

- HDL files for the MSS components, including timing shells for synthesis HDL files are automatically managed by the Libero SoC and passed to the Synthesis and Simulation tools.

- EFC File: Contains your eNVM client data The EFC content is included in your final programming file.

- Firmware drivers and memory maps are exported into the project>\firmware\ directory Libero SoC automatically generates a Software IDE project that includes your Firmware drivers. If you are not using a software project automatically created by Libero, you can import this directory into your Software IDE project.

- Testbench HDL and BFM script for the MSS design: These files are managed by Libero SoC and automatically passed to the Simulation tool.

- PDC files for the MSS and the top-level design: These files are managed by Libero SoC and automatically integrated during Compile and Layout.

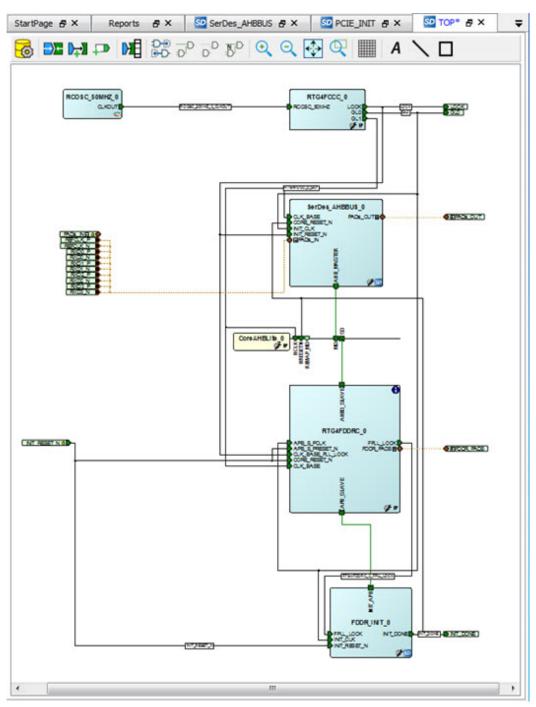

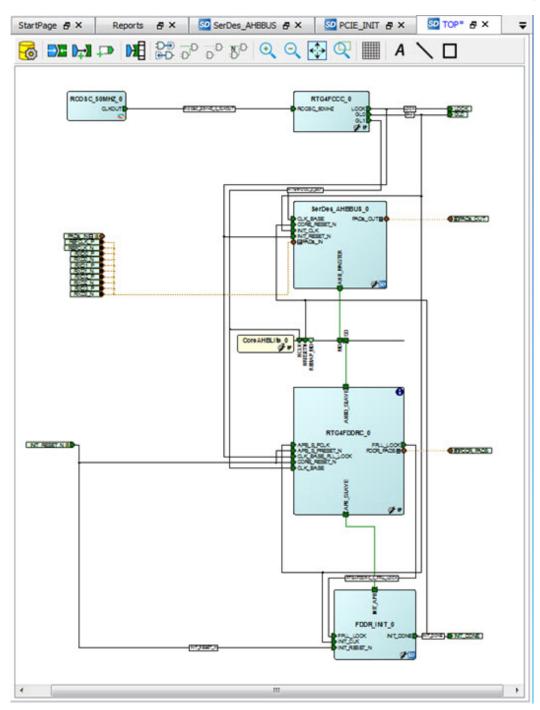

# About SmartDesign

SmartDesign is a visual block-based design creation tool for instantiation, configuration and connection of Microsemi IP, user-generated IP, custom/glue-logic HDL modules. The final result is a design-rule-checked and automatically abstracted synthesis-ready HDL file. A generated SmartDesign can be the entire FPGA design or a component subsystem of a larger design.

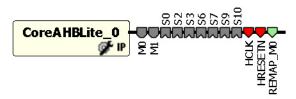

Instantiate IP cores, macros and HDL modules by dragging them from the <u>Catalog</u> onto the <u>Canvas</u>, where they are viewed as blocks in a functional block diagram. From the Canvas you can:

- · Configure your blocks

- · Make connections between your blocks

- Generate your SmartDesign

- This step generates the HDL and testbench files required to proceed with Synthesis and Simulation.

SmartDesign supports all Microsemi SoC product families.

# SmartDesign Design Flow

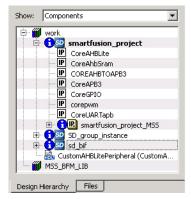

SmartDesign enables you to stitch together design blocks of different types (HDL, IP, etc.) and generate a top-level design. The Files tab lists your SmartDesign files in alphabetical order.

You can build your design using SmartDesign with the following steps:

**Step One – Instantiating components:** In this step you <u>add one or more building blocks</u>, HDL modules, components, and schematic modules from the project manager to your design. The components can be blocks, cores generated from the <u>core Catalog</u>, and IP cores.

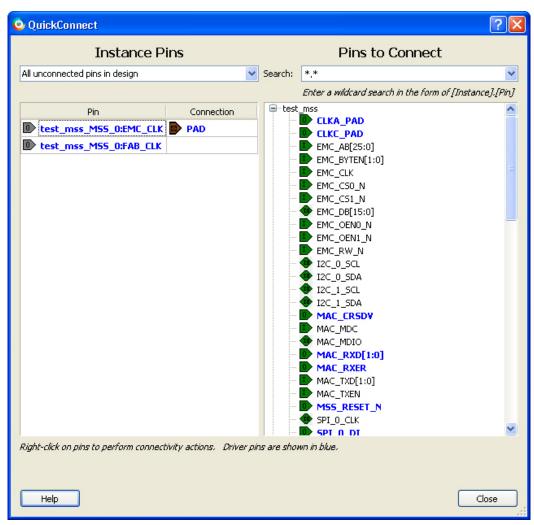

**Step Two – Connecting bus interfaces:** In this step, you can <u>add connectivity via standard bus interfaces</u> to your design. This step is optional and can be skipped if you prefer manual connections. Components generated from the <u>Catalog</u> may include pre-defined interfaces that allow for <u>automatic connectivity</u> and design rule checking when used in a design.

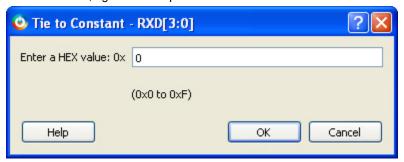

**Step Three – Connecting instances:** The <u>Canvas</u> enables you to create manual connections between ports of the instances in your design. Unused ports can be <u>tied off</u> to GND or VCC (disabled); input buses can be <u>tied to a constant</u>, and you can leave an output open by <u>marking it as unused</u>.

**Step Four – Generating the SmartDesign component:** In this step, you generate a top-level (Top) component and its corresponding HDL file. This component can be used by downstream processes, such as synthesis and simulation, or you can add your SmartDesign HDL into another SmartDesign.

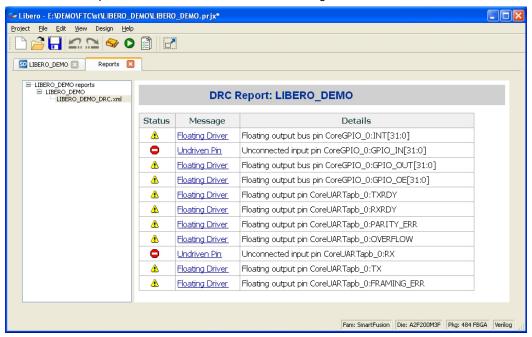

When you generate your SmartDesign the <u>Design Rules Check</u> verifies the connectivity of your design; this feature adds information to your report; design errors and warnings are organized by type and message and displayed in your Datasheet / Report.

You can save your SmartDesign at any time.

# Using Existing Projects with SmartDesign

You can use existing Libero SoC projects with available building blocks in the project to assemble a new SmartDesign design component. You do not have to migrate existing top-level designs to SmartDesign and there is no automatic conversion of the existing design blocks to the SmartDesign format.

# SmartDesign Frequently Asked Questions

The collection of SmartDesign Frequently Asked Questions are useful for anyone that is new to SmartDesign. All the information listed below is explained in detail in other sections of the help, but the information is summarized here for easy reference. Click any question to go to the corresponding explanation.

### **General Questions**

What is SmartDesign?

<u>SmartDesign</u> is a design entry tool. It's the first tool in the industry that can be used for designing System on a Chip designs, custom FPGA designs or a mixture of both types in the same design. A SmartDesign can be the entire FPGA design, part of a larger SmartDesign, or a user created IP that can be stored and reused multiple times. It's a simple, intuitive tool with powerful features that enables you to work at the abstraction level at which you are most comfortable.

It can connect blocks together from a variety of sources, verify your design for errors, manage your memory map, and generate all the necessary files to allow you to simulate, synthesize, and compile your design.

How do I create my first SmartDesign?

In the Libero SoC Project Manager Design Flow window, under Create Design, double-click **Create SmartDesign**.

# Instantiating Into Your SmartDesign

• Where is the list of Cores that I can instantiate into my SmartDesign?

The list of available cores is displayed in the <u>Catalog</u>. This catalog contains all DirectCore IP, Design Block cores, and macros.

· How do I instantiate cores into my SmartDesign?

Drag and drop the core from the <u>Catalog</u> onto your SmartDesign <u>Canvas</u>. An instance of your Core appears on the Canvas; double-click to configure it.

I have a block that I wrote in VHDL (or Verilog), can I use that in my SmartDesign?

Yes! Import your HDL file into the Project Manager (File > Import Files). After you do this, your HDL module will appear in the Project Manager <u>Hierarchy</u>. Then, drag-and-drop it from the Hierarchy onto your SmartDesign Canvas.

• My HDL module has Verilog parameters or VHDL generics declared, how can I configure those in SmartDesign?

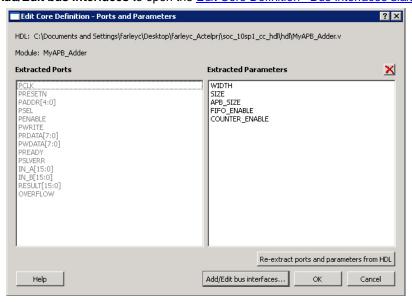

If your HDL module contains configurable parameters, you must create a 'core' from your HDL before using it in SmartDesign. Once your HDL module is in the Project Manager Design Hierarchy, right-click it and choose **Create Core from HDL**. You will then be allowed to add bus interfaces to your module if necessary. Once this is complete, you can drag your new HDL+ into the SmartDesign Canvas and configure your parameters by double-clicking it.

# Working in SmartDesign

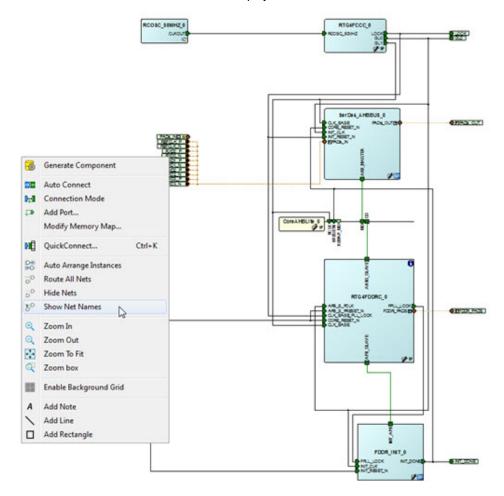

· How do I make connections?

Let SmartDesign do it for you. Right-click the Canvas and choose Auto Connect.

Auto Connect didn't connect everything for me, how do I make manual connections?

Enter **Connection Mode** and click and drag from one pin to another. Click the Connection Mode button in the Canvas to enter Connection Mode.

Alternatively:

- 1. Select the pins you want connected by using the mouse and the CTRL key.

- 2. Right-click one of the selected pins and choose Connect.

- How do I connect a pin to the top level?

Right-click the pin and choose **Promote to Top Level**. You can even do this for multiple pins at a time, just select all the pins you want to promote, right-click one of the pins and choose **Promote to Top Level**. All your selected pins will be promoted to the top level.

Oops, I just made a connection mistake. How do I disconnect two pins?

Use CTRL+Z to undo your last action. If you want to undo your 'undo', hit redo (CTRL+Y).

To disconnect pins you can:

- Right-click the pin you want to disconnect and choose Disconnect

- · Select the net and hit the delete key

- I need to apply some simple 'glue' logic between my cores. How do I do that?

For basic inversion of pins, you can right-click a pin and choose **Invert**. An inverter will be placed at this pin when the design is generated. You can also right-click a pin and choose Tie Low or Tie High if you want to connect the pin to either GND or VCC.

To tie an input bus to a constant, right-click the bus and choose **Tie to Constant**. To mark an output pin as unused, right-click the pin and choose **Mark as Unused**.

To clear these, just right-click on the pin again and choose Clear Attribute.

My logic is a bit more complex than inversion and tie offs - what else can I do?

You have full access to the library macros, including AND, OR, and XOR logic functions. These are located in the <u>Catalog</u>, listed under Macro Library. Drag the logic function you want onto your SmartDesign Canvas.

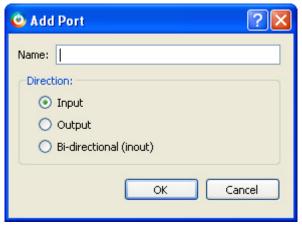

· How do I create a new top level port for my design?

Click the Add Port button in the Canvas toolbar

· How do I rename one of my instances?

Double-click the instance name on the Canvas and it will become editable. The instance name is located directly above the instance on the Canvas.

How do I rename my top level port?

Right-click the port you want to rename and choose Modify Port.

· How do I rename my group pins?

Right-click the group pin you want to rename and choose Rename Group.

I need to reconfigure one of my Cores, can I just double-click the instance?

Yes.

I want more Canvas space to work with!

Maximize your workspace (CTRL-W), and your Canvas will maximize within the Project Manager. Press CTRL-W again if you need to see your Hierarchy or Catalog.

# Working with Processor-Based Designs in SmartDesign

· How do I connect my peripherals to the bus?

Click **Auto Connect** and it will help you build your bus structure based on the processor and peripherals that you have instantiated.

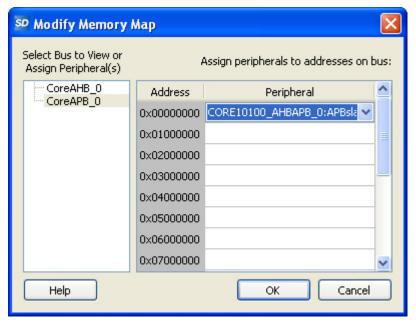

· But I need my peripheral at a specific address or slot.

Right-click the Canvas and choose **Modify Memory Map** to invoke the Modify Memory Map dialog that enables you to set a peripheral to a specific address on the bus.

The bus core will show the slot numbers on the bus interface pins. These slot numbers correspond to a memory address on the bus.

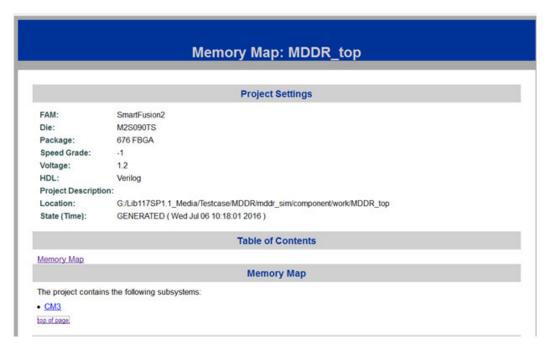

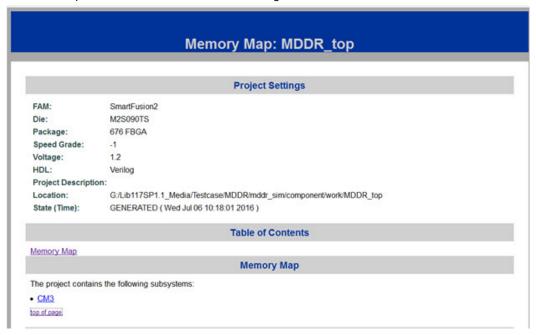

Verify that your peripheral is mapped to the right bus address by viewing your design's Memory Map.

#### . How do I view the Memory Map of my design?

Generate your project and open datasheet in the Report View.

The memory map section will also show the memory details of each peripheral, including any memory mapped registers.

#### • How do I simulate my processor design?

SmartDesign automatically generates the necessary Bus Functional Model (BFM) scripts required to simulate your processor based design. A top level testbench for your SmartDesign is generated automatically as well.

Create your processor design, generate it, and you will be able to simulate it in ModelSim.

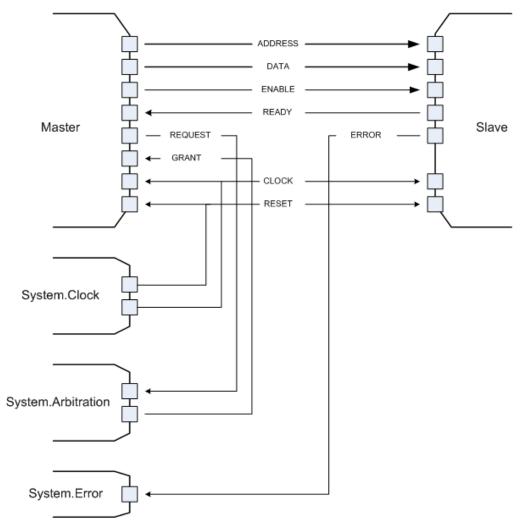

#### I have my own HDL block that I want to connect as a peripheral on the AMBA bus. How can I do that?

SmartDesign supports automatic creation of data driven configurators based on HDL generics/parameters.

If your block has all the necessary signals to interface with the AMBA bus protocol (ex. address, data, control signals):

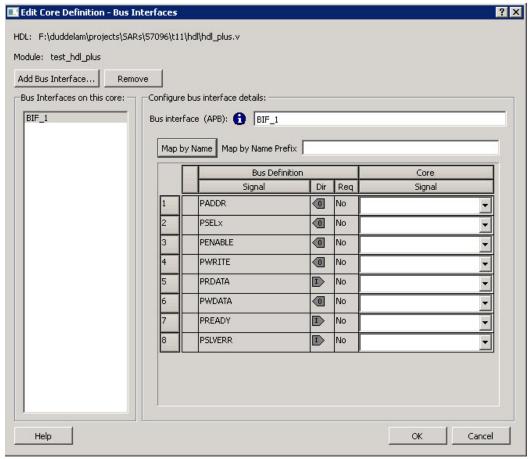

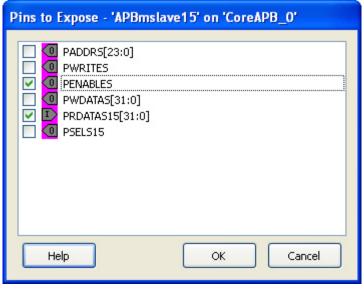

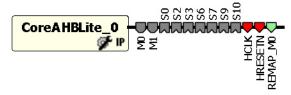

- Right-click your custom HDL block and choose Create Core from HDL. The Libero SoC creates your core and asks if you want to add bus interfaces.

- 2. Click **Yes** to open the Edit Core Definition dialog box and add bus interfaces. Add the bus interfaces as necessary.

- 3. Click **OK** to continue.

Now your instance has a proper AMBA bus interface on it. You can manually connect it to the bus or let Auto Connect find a compatible connection. See the <u>DirectCore Advanced Microcontroller Bus Architecture - Bus Functional Model User's Guide</u> for more information on CoreAMBA BFM commands.

#### · How do I generate the firmware drivers for my design?

SmartDesign automatically finds all the compatible firmware drivers based on your peripherals and processor. You can view the list of firmware drivers that the design found by going to the design flow and choosing <a href="View/Configure Firmware Cores">View/Configure Firmware Cores</a>.

#### • How do I start writing my application code for my design?

Libero SoC simplifies the embedded development process by automatically creating the workspace and project files for the Software IDE that you specify in the Tools profile.

Once you have generated your design, the firmware and workspace files will automatically be created. Click **Write Application Code** in the Design Flow tab and the Software IDE tool will open your design's workspace files.

### VHDL Construct Support in SmartDesign

What VHDL constructs do you support?

VHDL types Record, Array, Array of Arrays, Integer and Unsigned are supported on entity ports of imported VHDL files - these are treated as special types in Libero.

How can I import files with VHDL Special Types into SmartDesign?

To work with a VHDL file with Special Types you must:

- Drag and drop the entity into SmartDesign and connect it just as you would with any other SmartDesign instance.

- Generate the Mapping File (meta.out):

Navigate to the Design Hierarchy view, under the current SmartDesign.

Right-click every VHDL file or every top hierarchical file and choose Create Mapping File (VHDL).

- 3. Generate the SmartDesign

- 4. Continue with the Libero SoC Design Flow steps (Synthesis, Simulation, etc.)

If you do not generate the Mapping File, and try to Generate your SmartDesign, you will see the following error in the log window:

Error: Select the HDL file in the Design Hierarchy and right-click the HDL file and choose Create Mapping File(VHDL) because at least one entity port is of type Array or Record.

The above is reported only if the entity port is of type Record, Array, Array of Array, or Unsigned.

· What is the purpose of the mapping file?

The mapping file contains the mapping information between the SmartDesign ports and original user-specified data types of ports in design files, and is used for type casting of signals during design generation.

Where will the mapping file meta.out be generated?

The file is generated in your \$project\_dir/hdl folder. This file will be used to during SmartDesign generation.

What are the VHDL special types that are not generated automatically?

The following types are not automatically generated from the right-click menu option **Create Mapping File(VHDL)**:

- · Array of array is not supported

- · Array of record is not supported

- Enum in range of array is not supported.

- · Constants are not supported.

- · Buffer output ports are not supported

#### What do I do if I am using VHDL types that are not generated automatically?

You must manually write the mapping information in the meta.out file for unsupported types (types which are not generated automatically) in the prescribed format. Click the link to see an example.

- Integer

- Unsigned

- Array and Array of Arrays

- Record

- · What is the meta.out file format?

See the meta.out file format topic for more information.

# Making your Design Look Nice

- Can the tool automatically place my instances on the Canvas to make it look nice? Yes. Right-click the Canvas white space and choose Auto Arrange Instances.

- My design has a lot of connections, and the nets are making my design hard to read. What do I do?

You can disable the display of the nets in the menu bar (RMC > Hide Nets). This automatically hides all the nets in your design.

You can still see how pins are connected by selecting a connected pin, the net will automatically be visible again.

You can also selectively show certain nets, so that they are always displayed, just right click on a connected pin and choose **Show Net**.

My instance has too many pins on it; how can I minimize that?

<u>Try grouping functional or unused pins together</u>. For example, on the CoreInterrupt there are 8 FIQSource\* and 32 IRQSource\* pins, group these together since they are similar in functionality.

To group pins: Select all the pins you want to group, then right-click one of the pins and choose **Add pins to group**.

If a pin is in a group, you are still able to use it and form connections with it. Expand the group to gain access to the pin.

• Oops, I missed one pin that needs to be part of that group? How do I add a pin after I already have the group?

Select the pin you want to add and the group pin, right-click and choose **Add pins to <name> group**.

• I have a pin that I don't want inside the group, how do I remove it?

Right-click the pin and choose **Ungroup selected pins**.

How can I better see my design on the Canvas?

There are zoom icons in the Canvas toolbar. Use them to Zoom in, Zoom out, Zoom to fit, and Zoom selection. You can also maximize your workspace with CTRL-W.

# Generating your Design

- Ok, I'm done connecting my design, how do I 'finish' it so that I can proceed to synthesis?

In the Canvas toolbar, click the Generate Project icon .

- I get a message saying it's unable to generate my SmartDesign due to errors, what do I do?

What is the Design Rules Check?

The Design Rules Check is included in your Report View. It lists all the errors and warnings in your design, including unconnected input pins, required pin connections, configuration incompatibilities between cores, etc.

Errors are shown with a small red stop sign and must be corrected before you can generate; warnings may be ignored.

· What does this error mean? How do I fix it?

Review the <u>Design Rules Check topic</u> for an explanation of errors in the Design Rules Check and steps to resolve them.

How do I generate my firmware?

In the Design Flow window, expand **Handoff Design for Firmware Development** and double-click **Configure Firmware Cores**and **Export Firmware**.

# Creating a New SmartDesign Component

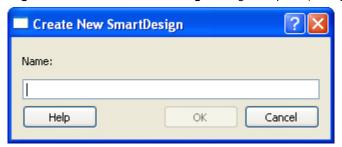

From the File menu, choose New > SmartDesign or in the Design Flow window double-click Create SmartDesign. The Create New SmartDesign dialog box opens (see figure below).

Figure 5 · Create New SmartDesign Dialog Box

2. Enter a component name and click **OK**. The component appears in the <u>Hierarchy</u> tab of the Design Explorer. Also, the main window displays the design <u>Canvas</u>.

Note: The component name must be unique in your project.

# Opening an Existing SmartDesign Component

To open an existing component do one of the following:

Click the **Design Hierarchy** tab and double-click the component you want to open.

The main window displays the SmartDesign Canvas for the SmartDesign component.

# Saving/Closing a SmartDesign Component

To save the current SmartDesign design component, from the **File** menu, choose **Save** <component\_name>. Saving a SmartDesign component only saves the current state of the design; to generate the HDL for the design refer to <u>Generating a SmartDesign component</u>.

To close the current SmartDesign component without saving, from the **File** menu, choose **Close**. Select **NO** when prompted to save.

To save the active SmartDesign component with a different name use Save As. From the **File** menu choose **Save SD\_<filename> As**. Enter a new name for your component and click **OK**.

# Generating a SmartDesign Component

Before your SmartDesign component can be used by downstream processes, such as synthesis and simulation, you must generate it.

Click the Generate button to generate a SmartDesign component.

This will generate a HDL file in the directory <libero\_project>/components/<library>/<yourdesign>.

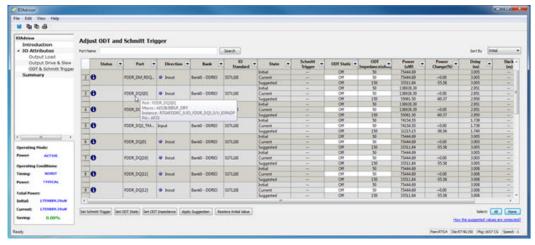

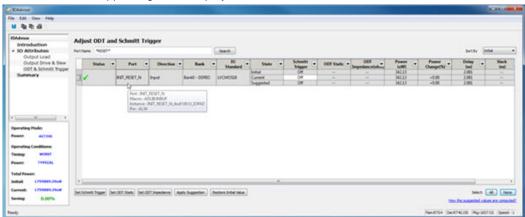

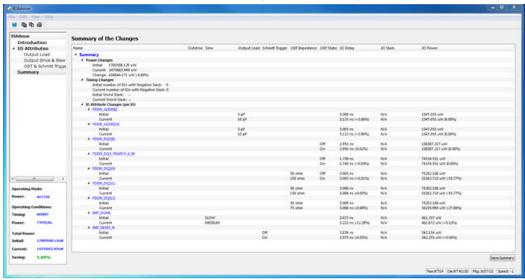

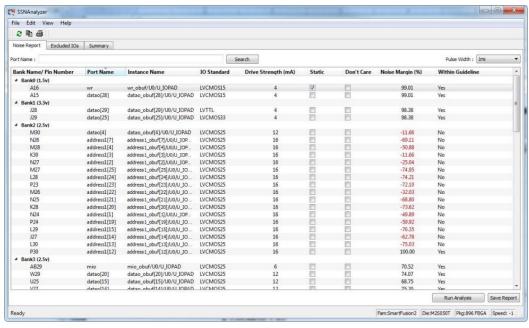

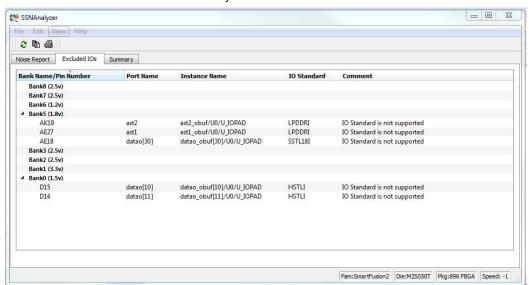

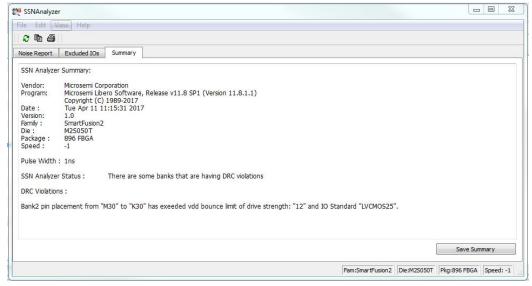

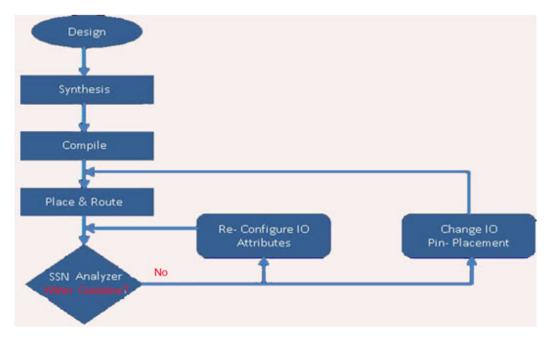

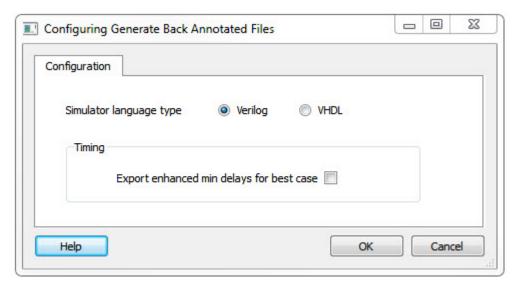

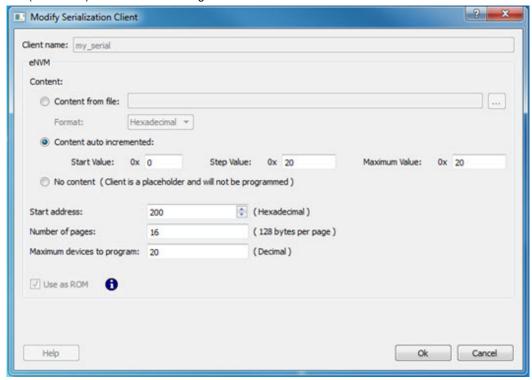

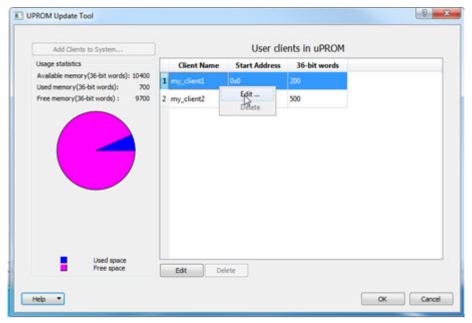

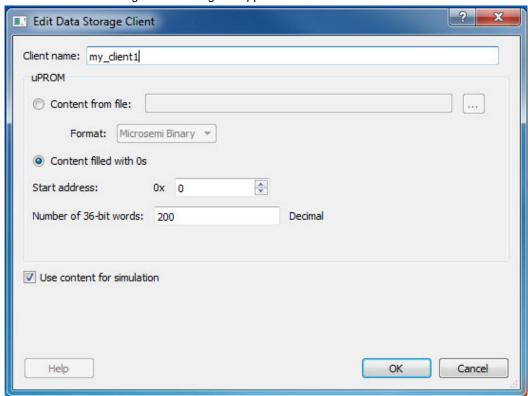

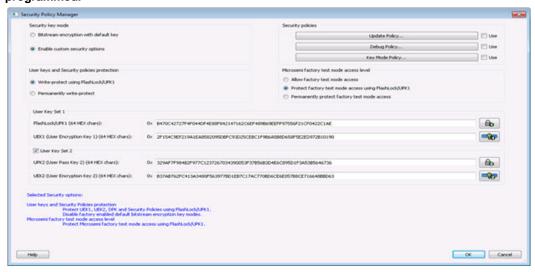

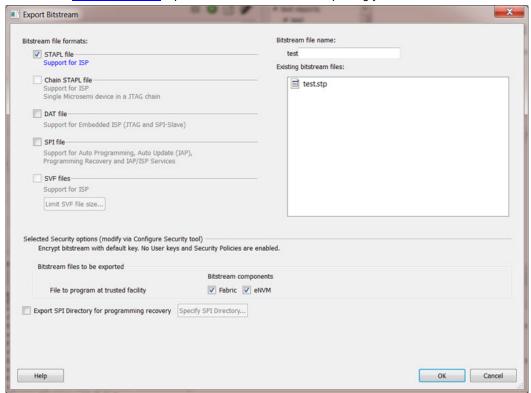

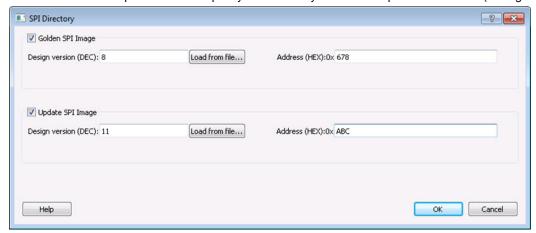

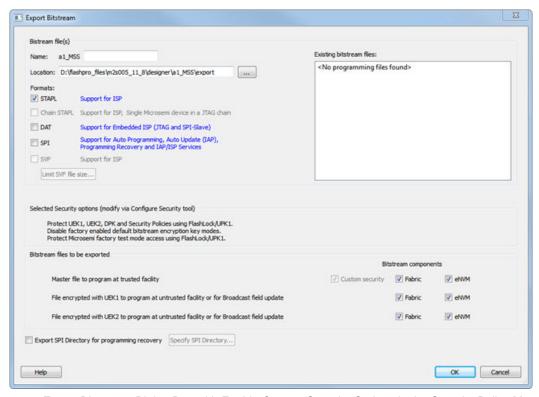

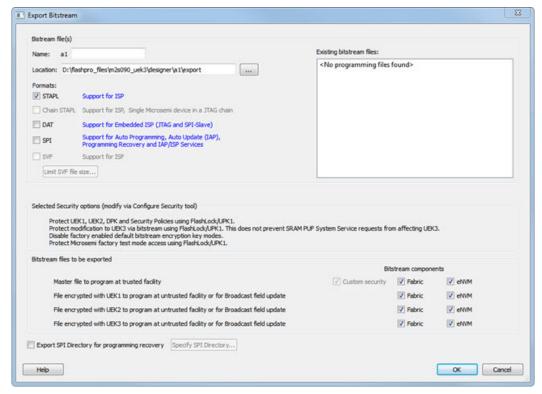

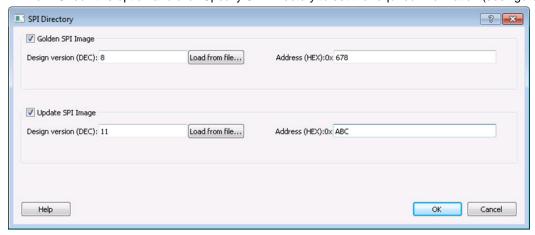

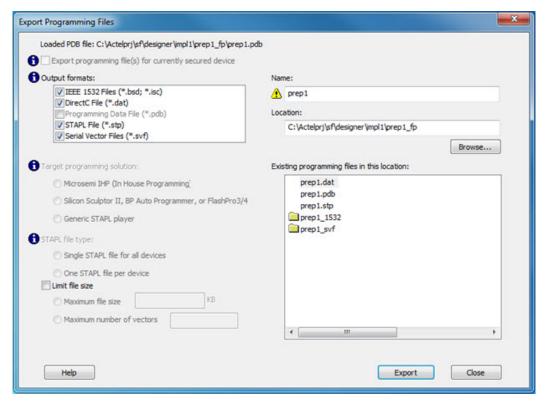

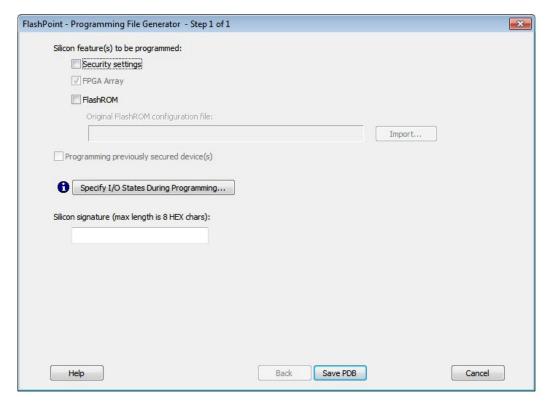

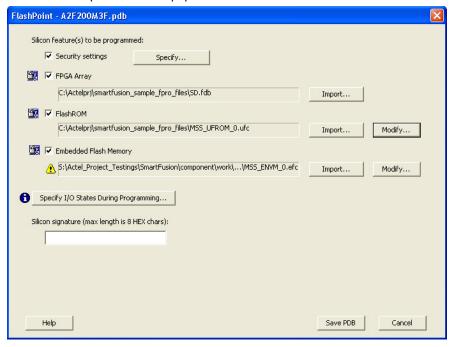

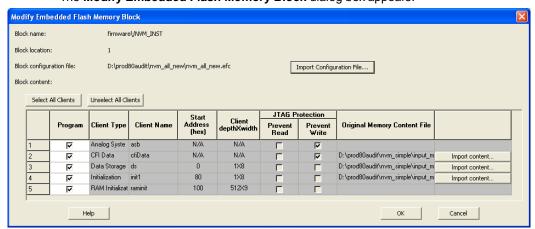

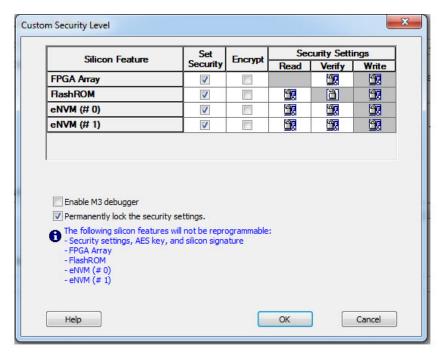

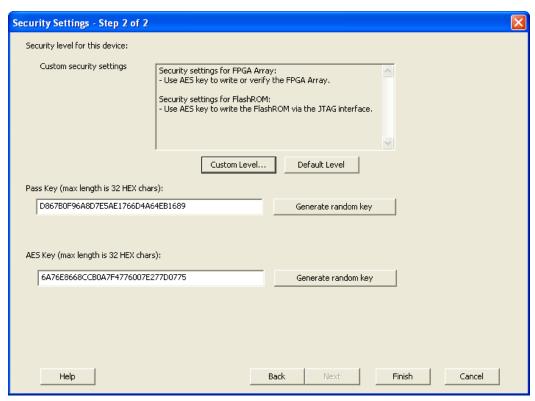

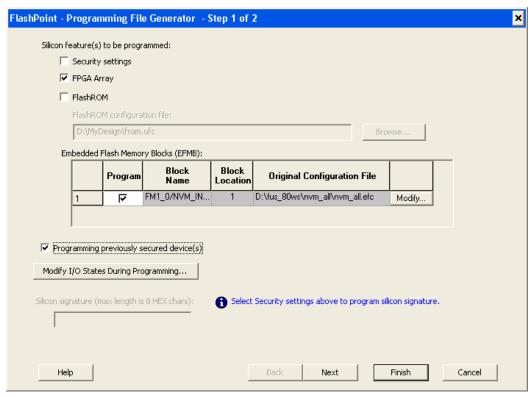

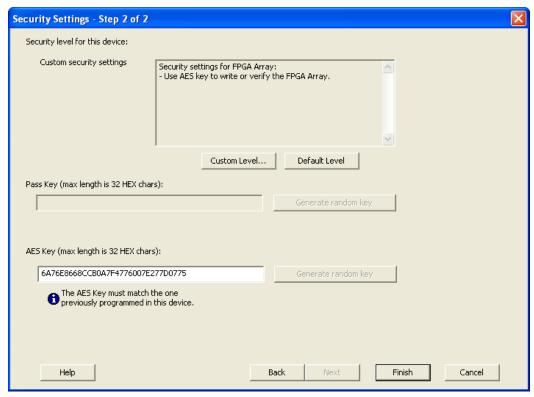

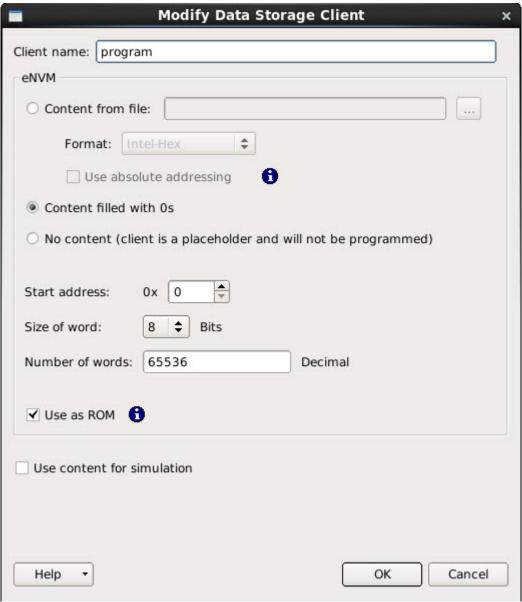

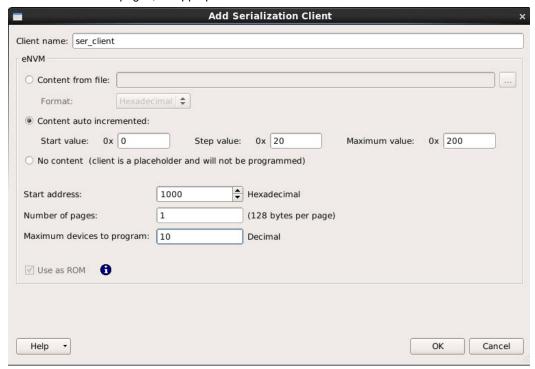

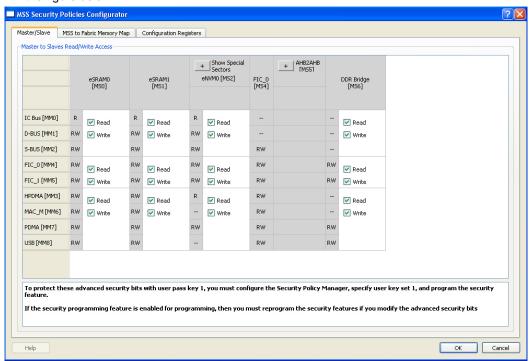

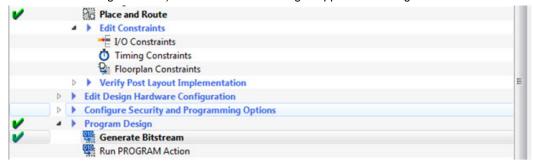

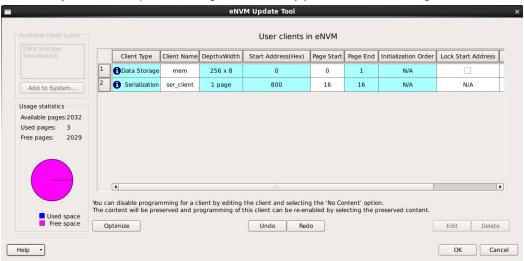

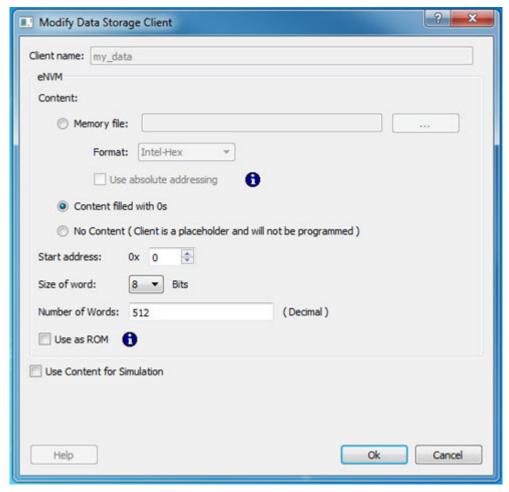

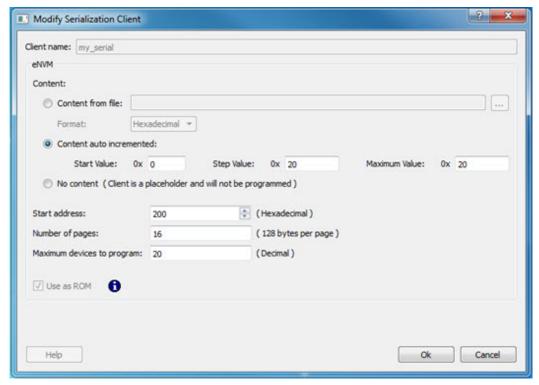

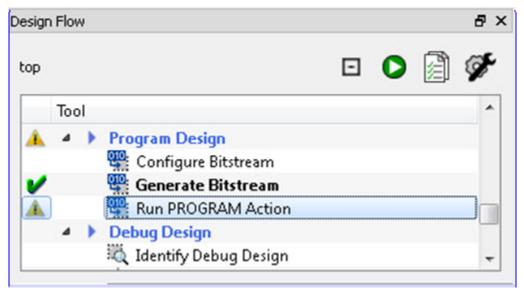

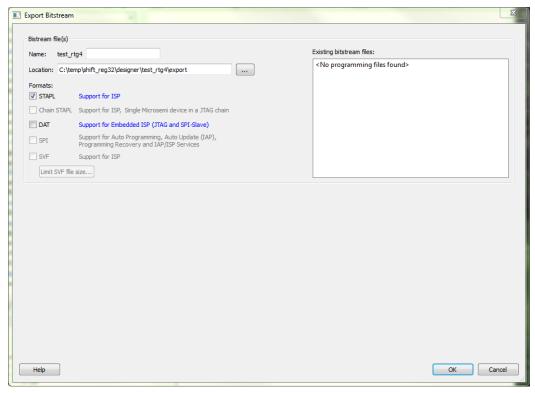

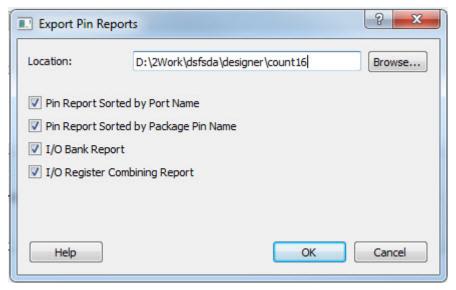

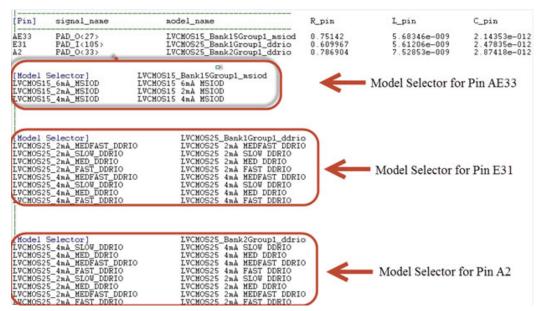

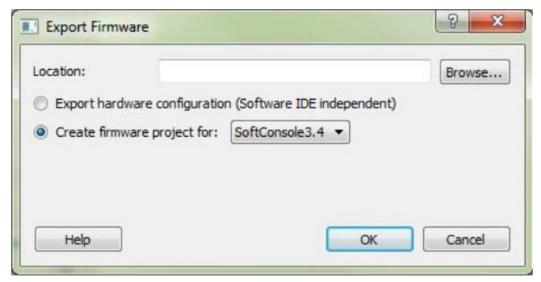

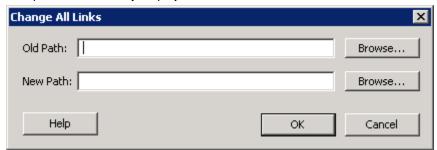

Note: The generated HDL file will be deleted when your SmartDesign design is modified and saved to ensure synchronization between your SmartDesign component and its generated HDL file.